Intel Desktop Board D925XCV/D925XBC Technical Product Specification

2.4 Fixed I/O Map

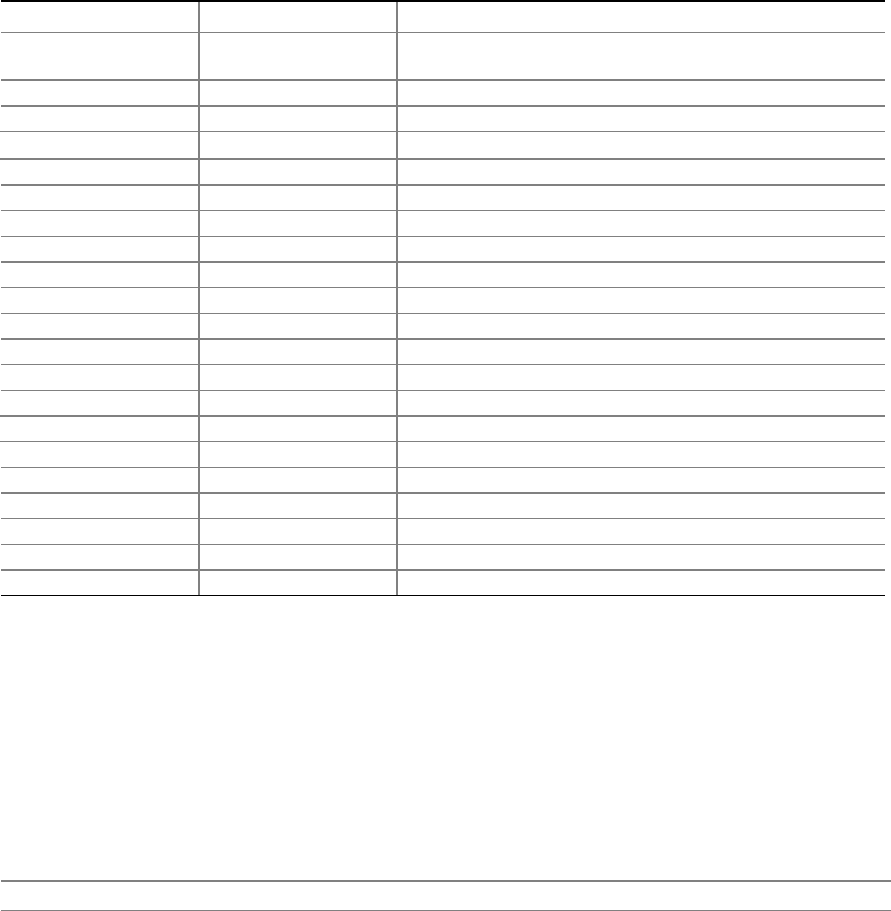

Table 13. I/O Map

Address (hex) Size Description

0000 - 00FF 256 bytes Used by the Desktop Board D925XCV/D925XBC. Refer to

the ICH6-R data sheet for dynamic addressing information.

0170 - 0177 8 bytes Secondary Parallel ATA IDE channel command block

01F0 - 01F7 8 bytes Primary Parallel ATA IDE channel command block

0228 - 022F

(Note 1)

8 bytes LPT3

0278 - 027F

(Note 1)

8 bytes LPT2

02E8 - 02EF

(Note 1)

8 bytes COM4

02F8 - 02FF

(Note 1)

8 bytes COM2

0374 - 0377 4 bytes Secondary Parallel ATA IDE channel control block

0377, bits 6:0 7 bits Secondary IDE channel status port

0378 - 037F 8 bytes LPT1

03E8 - 03EF 8 bytes COM3

03F0 - 03F5 6 bytes Diskette channel

03F4 – 03F7 1 byte Primary Parallel ATA IDE channel control block

03F8 - 03FF 8 bytes COM1

04D0 - 04D1 2 bytes Edge/level triggered PIC

LPTn + 400 8 bytes ECP port, LPTn base address + 400h

0CF8 - 0CFB

(Note 2)

4 bytes PCI Conventional bus configuration address register

0CF9

(Note 3)

1 byte Reset control register

0CFC - 0CFF 4 bytes PCI Conventional bus configuration data register

FFA0 - FFA7 8 bytes Primary Parallel ATA IDE bus master registers

FFA8 - FFAF 8 bytes Secondary Parallel ATA IDE bus master registers

Notes:

1. Default, but can be changed to another address range.

2. Dword access only.

3. Byte access only.

✏ NOTE

Some additional I/O addresses are not available due to ICH6-R address aliasing. The ICH6-R

data sheet provides more information on address aliasing.

For information about Refer to

Obtaining the ICH6-R data sheet Section 1.4 on page 19

58