Intel

®

Xeon™ Processor, Intel

®

E7520 Chipset, Intel

®

6300ESB ICH Development Kit User’s Manual 29

System Overview

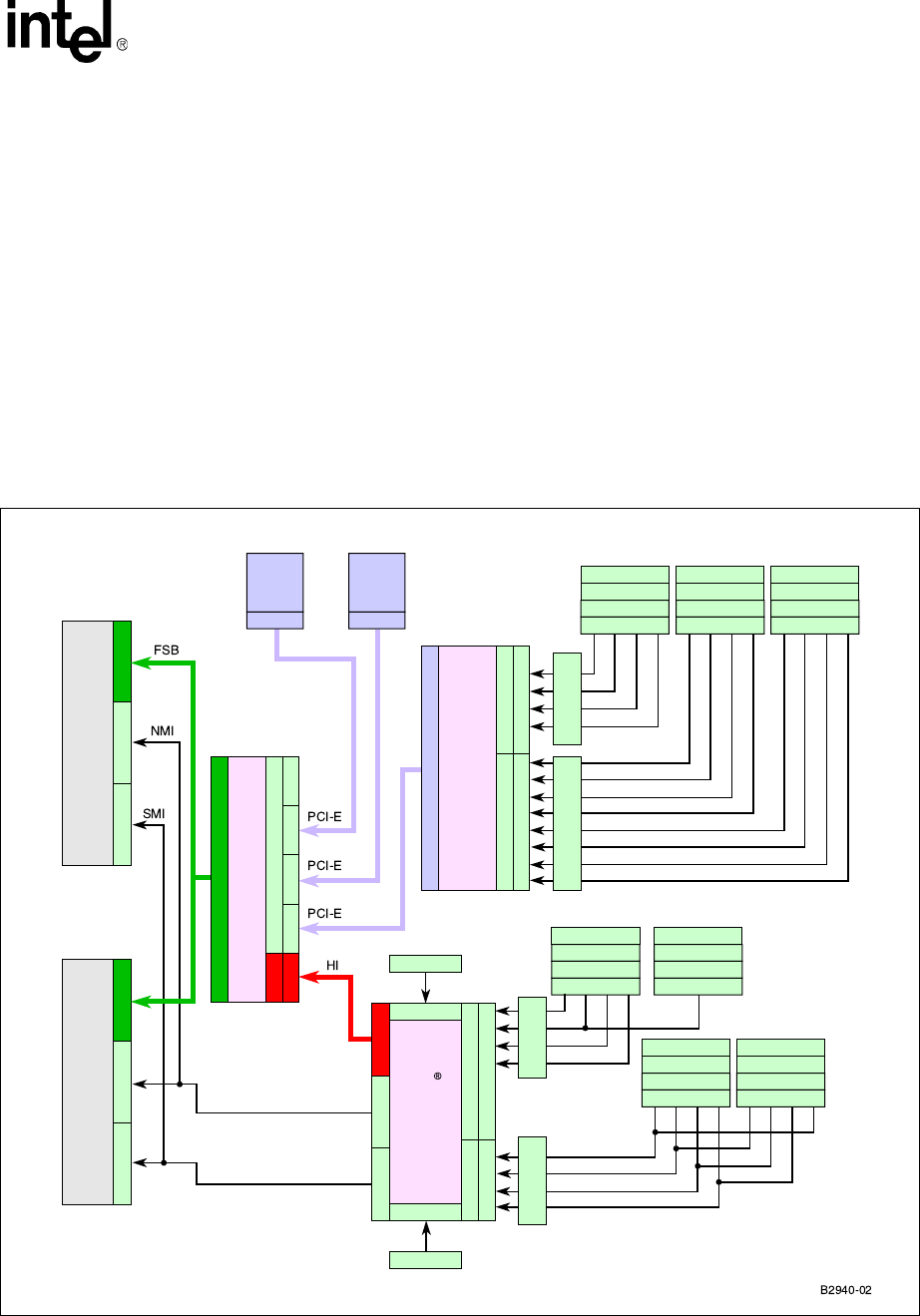

5.5 Platform IRQ Routing

Figure 9 shows that the Intel 6300ESB I/O Controller uses these segments:

• IRQ14 and 15 for IDE segment

• SERIRQ for SIOPIXRQ segment

• PCRIRQ for the PCI-X segment

• PIRQ for the PCI 32/33 segment

A Message Signalled Interrupt (MSI) scheme is used between the MCH and PXH over the PCI

Express bus. The PXH uses PAIRQ for the Channel A interface to PCI-X 64-bit/100 MHz

peripherals and PBIRQ for the Channel B interface to PCI-X 64/133. MSI and Non Maskable

Interrupt (NMI) are connected from the Intel 6300ESB I/O Controller to CPU0 and CPU1. The

platform also supports MSI for maskable and non-maskable interrupts.

Figure 9. IRQ Routing Diagram

MSI

PBIRQ

PCI-X SLOT

REQ/GNT: 0

IDSEL: AD17

ABCD

PAIRQ

0

1

2

3

0

1

2

3

4

5

6

7

PXH

CPU0

PCI-X SLOT

REQ/GNT: 0

IDSEL: AD17

ABCD

PCI-X SLOT

REQ/GNT: 1

IDSEL: AD18

ABCD

PCI-X 64/100

PCI-X 64/133

PCI-X 2.0

PIRQ

PCI-X SLOT

REQ/GNT: 0

IDSEL: AD16

ABCD

PXIRQ

A

B

C

D

A

B

C

D

E

F

G

H

Intel

6300ESB

I/O

Controller

Hub

Video

REQ/GNT: 1

IDSEL: AD17

PCI-X 64/66

PCI-X 32/33

NMISMI

IDE

IRQ14/15

SERIRQ

MSI

CPU0

NMISMI MSI

NMISMI MSI

SIO

A

PCI-X SLOT

REQ/GNT: 0

IDSEL: AD17

ABCD

PCI-X SLOT

REQ/GNT: 1

IDSEL: AD18

ABCD

FSB

MCH

PCI-E

MSI MSI MSI MSI

HI

MSI

PCI-E

4x

MSI

PCI-E

8x

MSI