121

CHAPTER 5 CPU ARCHITECTURE

5.4 Operand Address Addressing

The following various methods are available to specify the register and memory (addressing) which undergo

manipulation during instruction execution.

5.4.1 Implied addressing

[Function]

The register which functions as an accumulator (A and AX) in the general register is automatically (illicitly)

addressed.

Of the

µ

PD78054 and 78054Y subseries instruction words, the following instructions employ implied addressing.

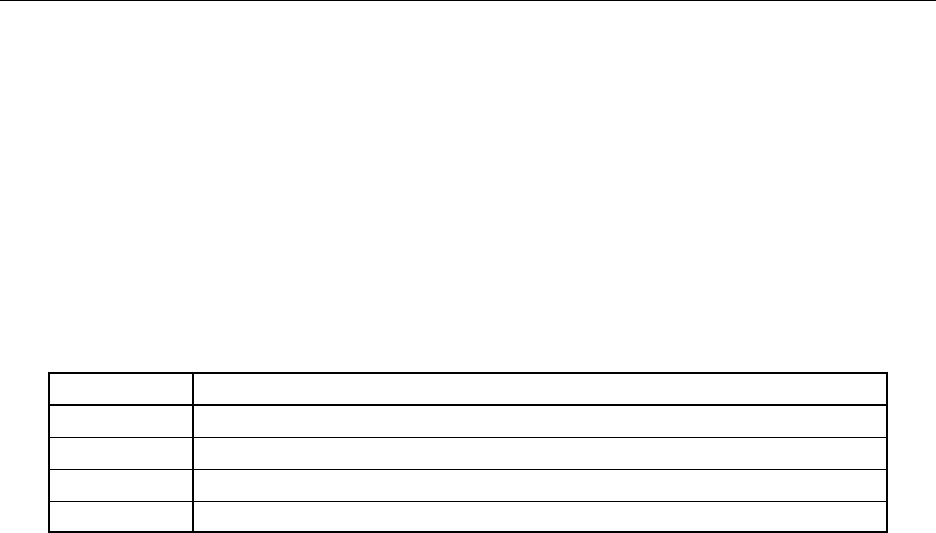

Instruction Register to be Specified by Implied Addressing

MULU A register for multiplicand and AX register for product storage

DIVUW AX register for dividend and quotient storage

ADJBA/ADJBS A register for storage of numeric values which become decimal correction targets

ROR4/ROL4 A register for storage of digit data which undergoes digit rotation

[Operand format]

Because implied addressing can be automatically employed with an instruction, no particular operand format is

necessary.

[Description example]

In the case of MULU X

With an 8-bit × 8-bit multiply instruction, the product of A register and X register is stored in AX. In this example,

the A and AX registers are specified by implied addressing.