Functional Specifications

2.2 CPU

Rev.1.00

Oct 09, 2008 2-3

REJ11J0021-0100

2

2.2 CPU

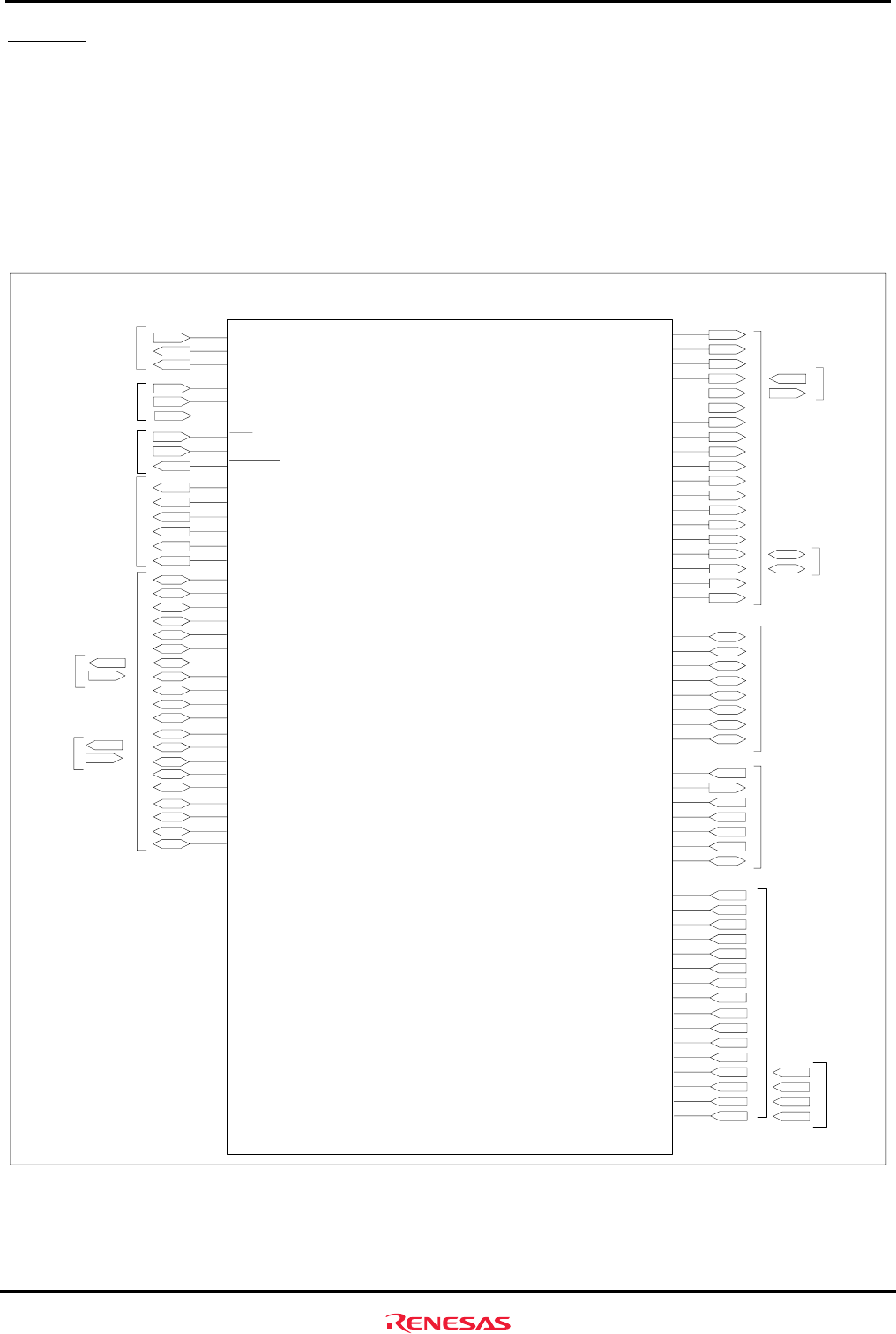

The M3A-HS37 is provided with the SH7137, the 32-bit RISC MCU operates with a maximum frequency of 80 MHz.

The SH7137 MCU is provided with a 256-KB flash memory, and a 16-KB RAM, which covers a wide range of applications

from data processing to equipment control.

The M3A-HS37 can be operated with a maximum CPU frequency of 80 MHz (external bus 40 MHz at maximum) using a 10.0

MHz of the input clock.

Figure 2.2.1 shows the SH7137 block diagram on the M3A-HS37.

EXTAL

XTAL

PA15/CK/TXD1/SSO

MD1

MD0

RES

NMI

WDTOVF

SH7137

Clock

Mode

SW

System

control

User

LEDs

User

DIP

switches

Address bus

SRAM/

/I/O port

Data bus

/SRAM

/Input port

H-UDI

PF0/AN0

PF1/AN1

PF2/AN2

PF3/AN3

PF4/AN4

PF5/AN5

PF6/AN6

PF7/AN7

PA0/RXD0/A0/POE0

PA1/TXD0/A1/POE1

PA2/SCK0/IRQ0/A2/POE2

PA3/RXD1/A3/IRQ1

PA4/TXD1/A4/IRQ2

PA5/SCK1/A5/IRQ3

PA10/A6/RXD0

PA11/ADTRG/A7/TXD0

PA12/A8/SCS/SCK0

PA13/A9/SSCK/SCK1

PA14/A10/SSI/RXD1

PE4/TIOC1A/A11/RXD1

PE5/TIOC1B/A12/TXD1

PE6/TIOC2A/A13/SCK1

PE7/TIOC2B/A14

PE8/TIOC3A/A15

PB2/IRQ0/POE0/TIC5VS/SCL/A16

PB3/IRQ1/POE1/TIC5V/SDA/A17

PB4/IRQ2/TIC5US/A18/POE4

PB5/IRQ3/TIC5U/A19/POE5

PD0/D0/RXD0

PD1/D1/TXD0

PD2/D2/SCK0

PD3/D3/RXD1

PD4/D4/TXD1

PD5/D5/SCK1

PD6/D6/RXD2

PD7/D7/TXD2

PE18/TIOC4AS/CS1/TDI

PE19/TIOC4BS/RD/TDO

PE17/TIOC3DS/CS0/TCK

PE20/TIOC4CS//TMS

PE21/TIOC4DS/WRL/TRST

PE16/TIOC3BS/WAIT/ASEBRKAK/ASEBRK

ASMD0

PE9/TIOC3B

PE11/TIOC3D

PE12/TIOC4A

PE13/TIOC4B/MRES

PE14/TIOC4C

PE15/TIOC4D/IRQOUT

FWE

PA9/WAIT/TCLKD/POE8/TXD2

PA8/WRL/TCLKC/POE6/RXD2

PA7/TCLKB/POE5/SCK2

PA6/RD/UBCTRG/TCLKA

PB0/BACK/TIC5WS/

PB1/BREQ/TIC5W

PB6/WAIT/CTx0

PB7/CS1/CRx0

PD8/SCK2/SSCK

PD9/SSI

PD10/SSO

PE0/TIOC0A

PE1/TIOC0B/RXD0

PE2/TIOC0C/TXD0

PE3/TIOC0D/SCK0

PE10/TIOC3C/CS0

PE12/TIOC4A

PE13/TIOC4B/MRES

PE14/TIOC4C

PE15/TIOC4D/IRQOUT

Control signal,

MTU2/2S,

interrupt,

etc

PF8/AN8

PF9/AN9

PF10/AN10

PF11/AN11

PF12/AN12

PF13/AN13

PF14/AN14

PF15/1N15

Serial

port

EEPROM

A/D

/Input port

RCAN

port

Serial

port

Figure 2.2.1 SH7137 Block Diagram