Functional Overview

2.3.2 Flash Memory M5M29KT331AVP (included as standard equipment)

Rev.1.00 June 1,2005 2-5

REJ11J0002-0100Z

2

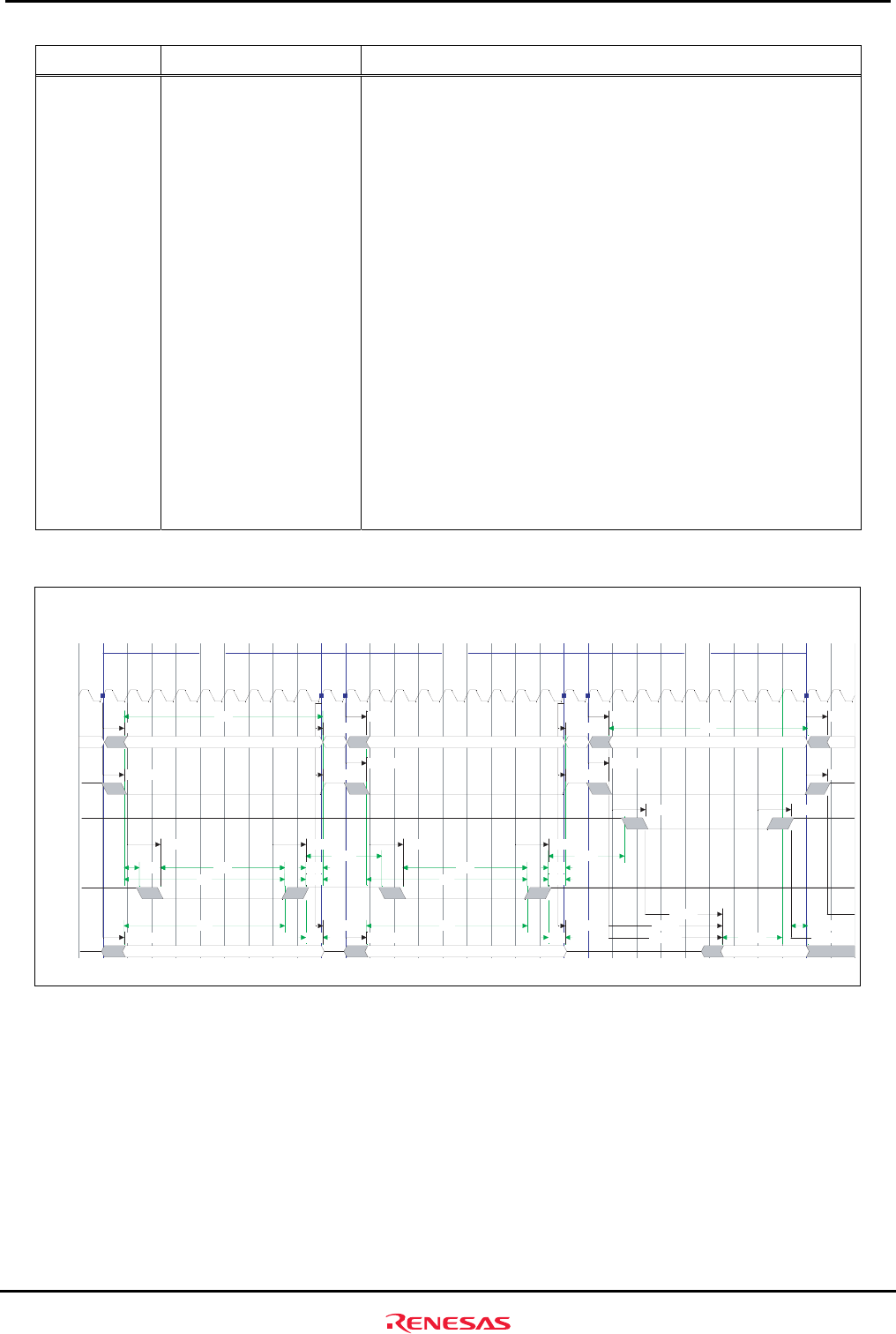

Table2.3.2 Examples for Bus State Controller Settings (Flash Memory Write/Read)

User Area Applicable Device Bus State Controller Settings

CS0 M5M29KT331AVP CS0 Space Bus Control Register : CS0BCR

Initial value : H'36DB 0600(when MD2= H and MD0=L)

Recommended set value : H'1000 0400

• Specify idle state in write to read and write to write intervals

IWW[2:0] = B'001: 1 idle cycles inserted

• Specify data bus

BSZ[1:0] = B'10 : 16-bit bus width

CS0 Space Wait Control Register (CS0WCR)

Initial value: H'0000 0500

Recommended set value : H'0000 0AC1

•

Address, CS0# assert -> RD#, WEn# assert delay cycle

SW[1:0] = B'01 : 1.5 cycles

• Specify access wait cycles

WR[3:0] = B'0110 : 5 cycles

• RD#, WEn# negate -> Address, CS0 negate delay cycle

HW[1:0] = B'01 : 1.5 cycles

<Write and Read Timing>

Write1 Write2 Read1

DATA DATA DATA

tDF(OE)ta(CE1)

ta(AD)

ta(OE)

tWDH1

tWDD1

tWDH1

tWDD1

tWED1tWED1tWED1tWED1

tRSDtRSD

tCSD

1

tCSD1

tCSD1

tCSD1

tCSD1tCSD1

tAD1tAD1

tAD1

tAD1

tAD1tAD1

tRDH1

tRDS1tDH

tDS

tDH

tDS

tOEH

tAHtAS

tCHtWP

tWPH

tWPtAH

tAS

tWPH

tCH

tWPtCS tWP

tRCtRC

tWCtWC

T1T2Tw4T1 Tw1 Tw2 Tw1 Tw2 T2 T1 Tw1 Tw2 Tw3 T2Tf Tf Taw1Taw1Th Th Th TfTw4Tw3 Tw3 Tw4 Tw5Tw5 Tw5

CKIO

A21-A1

CS0#

RD#

WE0#

D15-D0

Figure2.3.2 Flash Memory Read and Write Access Timing