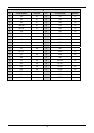

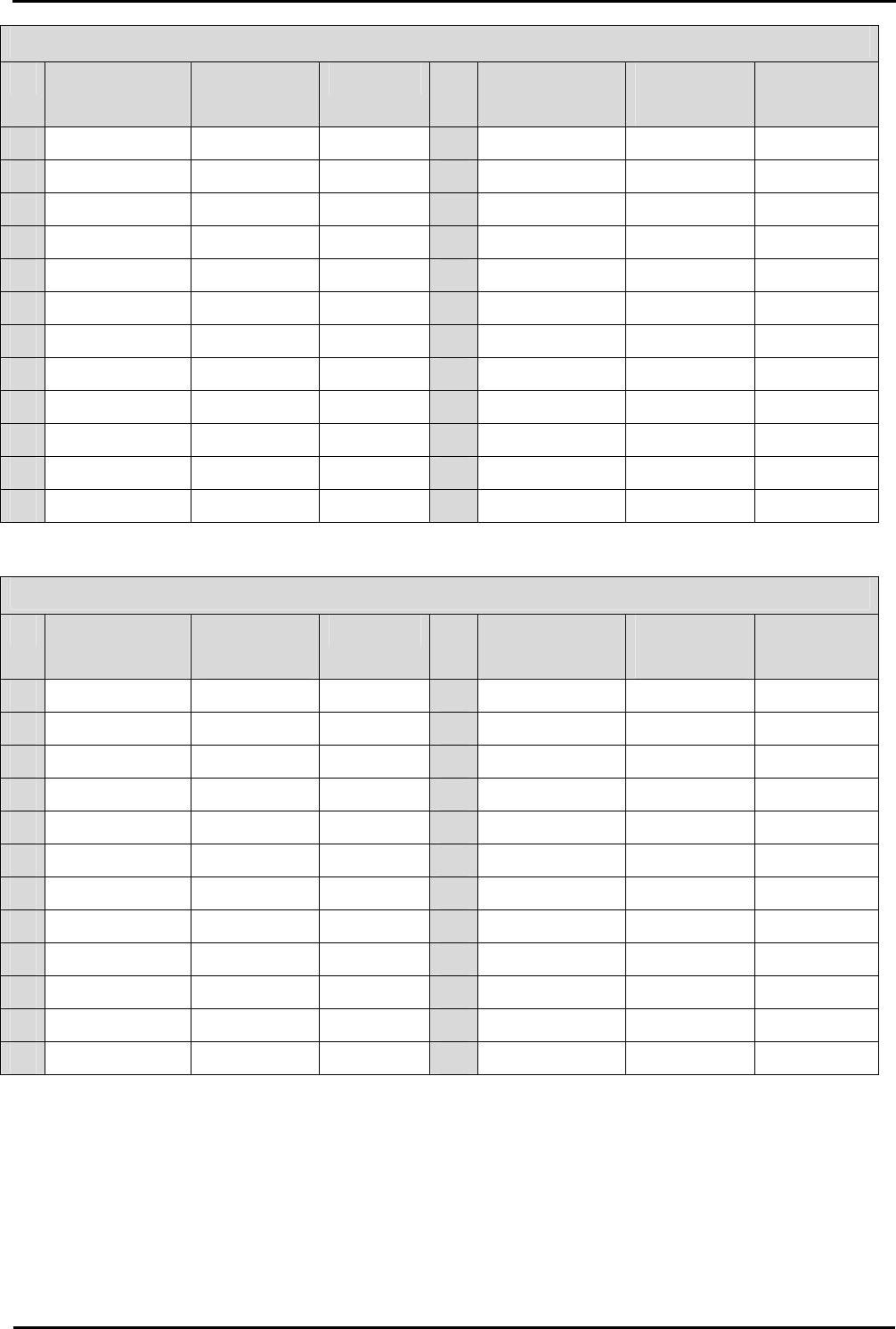

JA5

Pin Header Name CPU board

Signal Name

Device Pin Pin Header Name CPU board

Signal Name

Device Pin

1 AD4 AN4 90 13 Reserved

2 AD5 AN5 91 14 Reserved

3 AD6 AN6 92** (R8) 15 Reserved

4 AD7 AN7 93** (R11) 16 Reserved

5 CAN1TX CTx0 50 17 Reserved

6 CAN1RX CRx0 51 18 Reserved

7 CAN2TX CTx1 52 19 Reserved

8 CAN2TX CTx1 54 20 Reserved

9 Reserved 21 Reserved

10 Reserved 22 Reserved

11 Reserved 23 Reserved

12 Reserved 24 Reserved

Table 8-8: JA5 Standard Generic Header

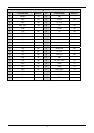

JA6

Pin Header Name CPU board

Signal Name

Device Pin Pin Header Name CPU board

Signal Name

Device Pin

1 DREQ DREQ3 46 13 Reserved

2 DACK DACK3 47 14 Reserved

3 TEND DTEND3 49 15 Reserved

4 STBYn DACT3 48 16 Reserved

5 RS232TX RS232TX (R60)**** 17 Reserved

6 RS232RX RS232RX (R70)**** 18 Reserved

7 SCIbRX RxD1 110 19 Reserved

8 SCIbTX TxD1 111 20 Reserved

9 SCIcTX TxD4 117 21 Reserved

10 SCIbCX SCK1 109 22 Reserved

11 SCIcCK SCK4 115 23 Reserved

12 SCIcRX RxD4 116 24 Reserved

Table 8-9: JA6 Standard Generic Header

**** This signal is only connected to the named link, which is not fitted to the board. For details refer to the RSKSH7201 circuit schematics

page 5

21