EMBEDDED FLASH MEMORY INTERFACE S3F8275X

16-2

USER PROGRAM MODE

This mode supports sector erase, byte programming, byte read and one protection mode (Hard lock protection).

The read protection mode is available only in Tool Program mode. So in order to make a chip into read protection,

you need to select a read protection option when you program an initial your code to a chip by using Tool Program

mode by using a programming tool.

The S3F8275X has the pumping circuit internally. Therefore, 12.5V into VPP (test) pin is not needed. To program

a flash memory in this mode several control registers will be used. There are four kind functions– programming,

reading, sector erase, hard lock protection.

FLASH MEMORY CONTROL REGISTERS (USER PROGRAM MODE)

Flash Memory Control Register

FMCON register is available only in user program mode to select the Flash Memory operation mode; sector erase,

byte programming, and to make the flash memory into a hard lock protection.

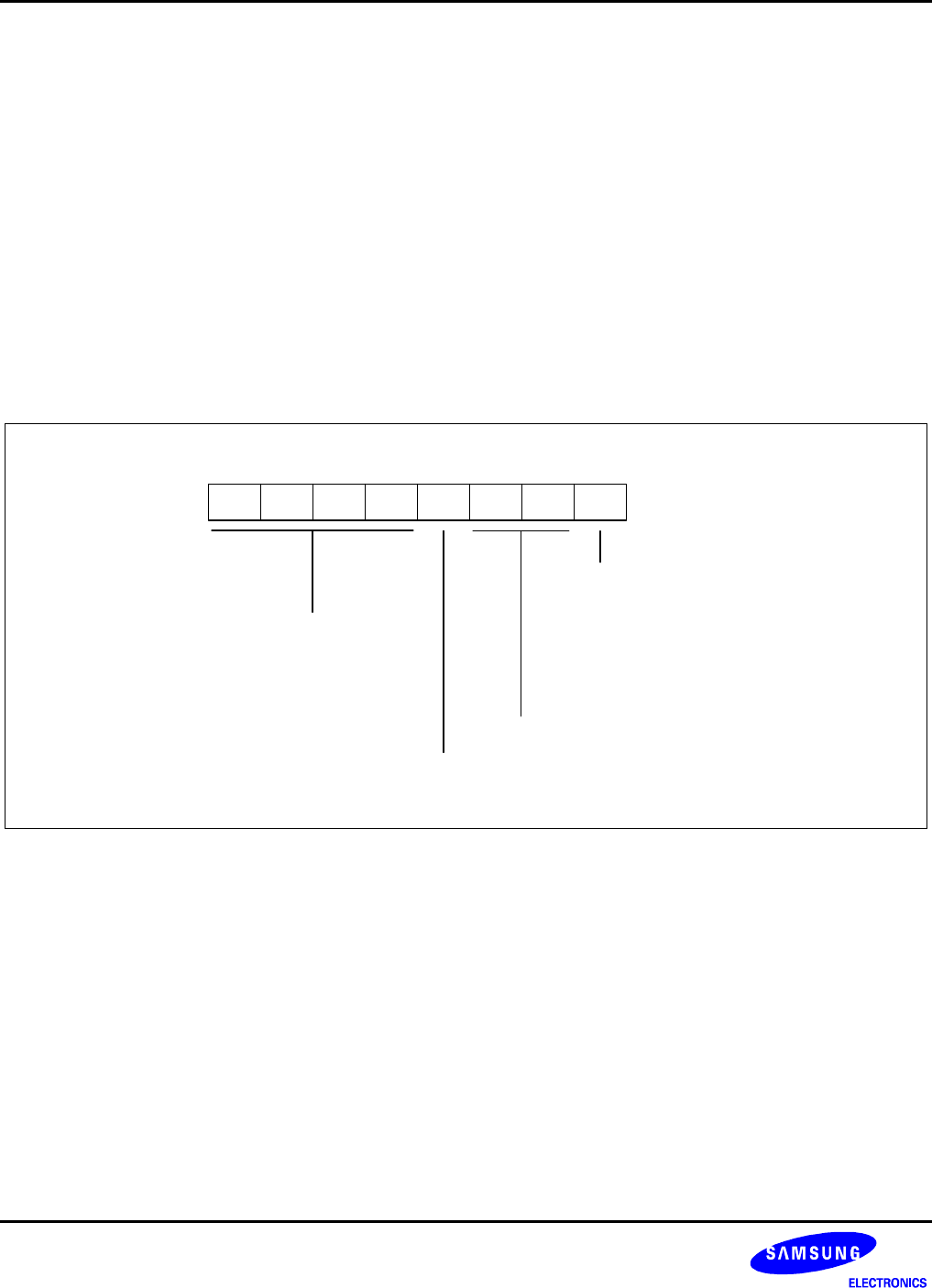

Flash Memory Control Register (FMCON)

F0H, Set 1, Bank 1, R/W

.7 .6 .5 .4 .3 .2 .1 .0MSB LSB

Flash operation start bit:

0 = Operation stop

1 = Operation start

(This bit will be cleared automatically

just after the corresponding operation

completed).

Sector erase status bit:

0 = Success sector erase

1 = Fail sector erase

Flash memory mode selection bits:

0101 = Programming mode

1010 = Sector erase mode

0110 = Hard lock mode

others = Not available

Not used for S3F8275X

Figure 16-1. Flash Memory Control Register (FMCON)

The bit 0 of FMCON register (FMCON.0) is a start bit for Erase and Hard Lock operation mode. Therefore,

operation of Erase and Hard Lock mode is activated when you set FMCON.0 to "1". Also you should wait a time of

Erase (Sector erase) or Hard lock to complete it's operation before a byte programming or a byte read of same

sector area by using "LDC" instruction. When you read or program a byte data from or into flash memory, this bit

is not needed to manipulate.

The sector erase status bit is read only. If an interrupt is requested during the operation of "Sector erase", the

operation of "Sector Erase" is discontinued, and the interrupt is served by CPU. Therefore, the sector erase status

bit should be checked after executing "Sector Erase". The "Sector Erase" operation is success if the bit is logic

"0", and is failure if the bit is logic "1".

NOTE: When the ID code, "A5H", is written to the FMUSR register. A mode of sector erase, user program, and hard lock may

be executed unfortunately. So, It should be careful of the above situation.