Si53xx-RM

Rev. 0.5 31

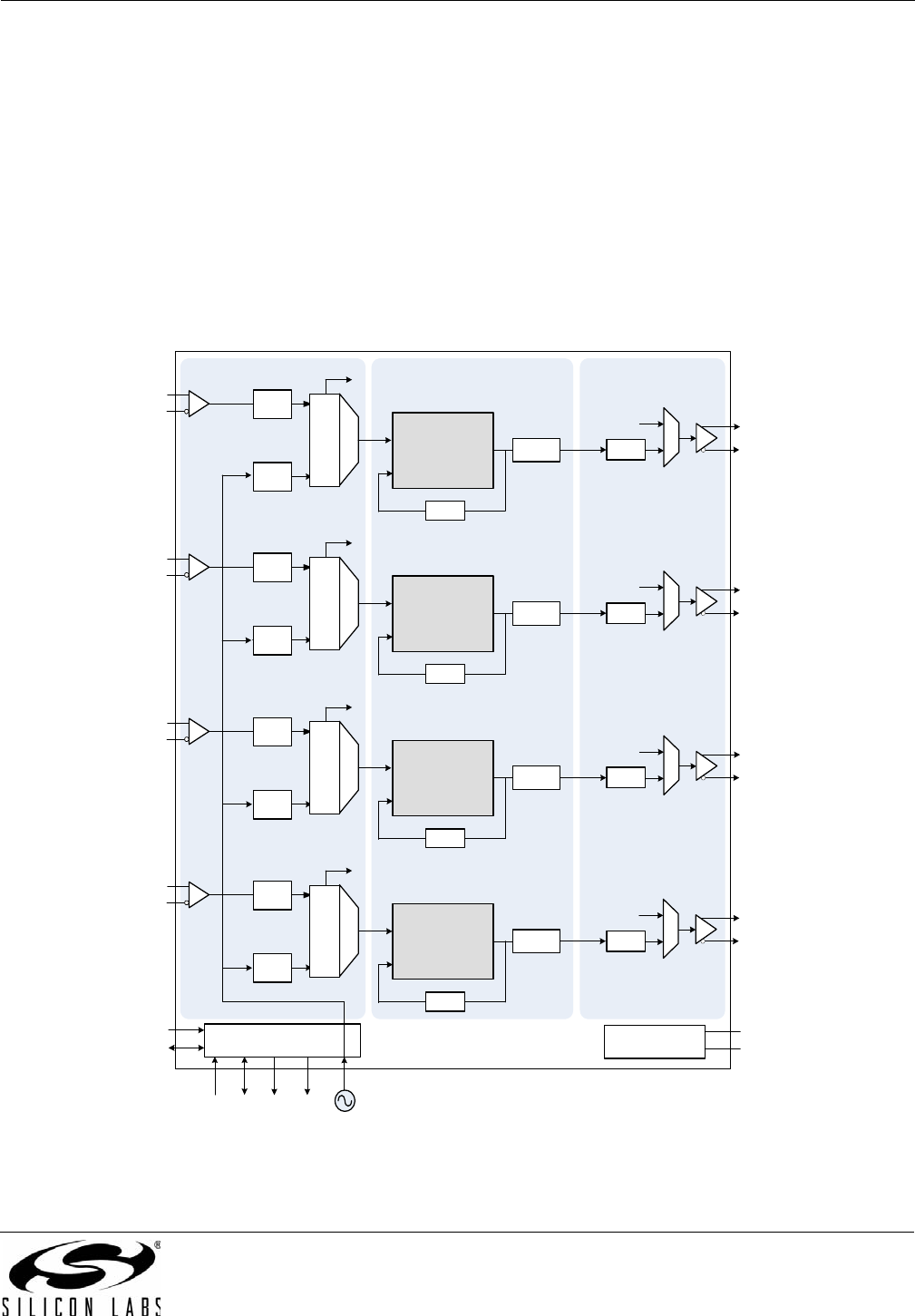

3.16. Si5375

The Si5375 is a highly integrated, 4-PLL jitter-attenuating precision clock multiplier for applications requiring sub 1

ps jitter performance. Each of the DSPLL® clock multiplier engines accepts an input clock ranging from 2 kHz to

710 MHz and generates an output clock ranging from 2 kHz to 808 MHz. Each DSPLL provides virtually any

frequency translation combination across this operating range. For asynchronous, free-running clock generation

applications, the Si5375’s reference oscillator can be used as a clock source for any of the four DSPLLs. The

Si5375 input clock frequency and clock multiplication ratio are programmable through an I2C interface. The Si5375

is based on Silicon Laboratories' third-generation DSPLL® technology, which provides any-frequency synthesis

and jitter attenuation in a highly integrated PLL solution that eliminates the need for external VCXO and loop filter

components. Each DSPLL loop bandwidth is digitally programmable from 60 Hz to 8 kHz, providing jitter

performance optimization at the application level. The device operates from a single 1.8 or 2.5 V supply with on-

chip voltage regulators with excellent PSRR. The Si5375 is ideal for providing clock multiplication and jitter

attenuation in high port count optical line cards requiring independent timing domains.

Figure 15. Si5375 Functional Block Diagram

CKIN1P_B

÷ N31

DSPLL

®

B

CKIN1N_B

÷ N32

f

OSC

÷ NC1_HS

Input

Monitor

f

3

÷ N2

Status / Control

PLL Bypass

High PSRR

Voltage Regulator

VDD_q

GND

Synthesis Stage

CKIN1P_A

CKOUT1N_A

÷ N31

DSPLL

®

A

CKIN1N_A

÷ N32

CKOUT1P_A

Output Stage

f

OSC

÷ NC1_HS

Input

Monitor

f

3

÷ N2

PLL Bypass

Input Stage

CKIN1P_D

÷ N31

DSPLL

®

D

CKIN1N_D

÷ N32

f

OSC

÷ NC1_HS

Input

Monitor

f

3

÷ N2

PLL Bypass

CKIN1P_C

÷ N31

DSPLL

®

C

CKIN1N_C

÷ N32

f

OSC

÷ NC1_HS

Input

Monitor

f

3

÷ N2

PLL Bypass

RSTL_q

CS_q

SCL SDA

LOL_q

IRQ_q

Low Jitter

XO or Clock

OSC_P/N

÷ NC1

PLL Bypass

CKOUT1N_B

÷ NC1

PLL Bypass

CKOUT1P_B

CKOUT1N_C

PLL Bypass

CKOUT1P_C

÷ NC1

CKOUT1N_D

÷ NC1

PLL Bypass

CKOUT1P_D