Si53xx-RM

Rev. 0.5 59

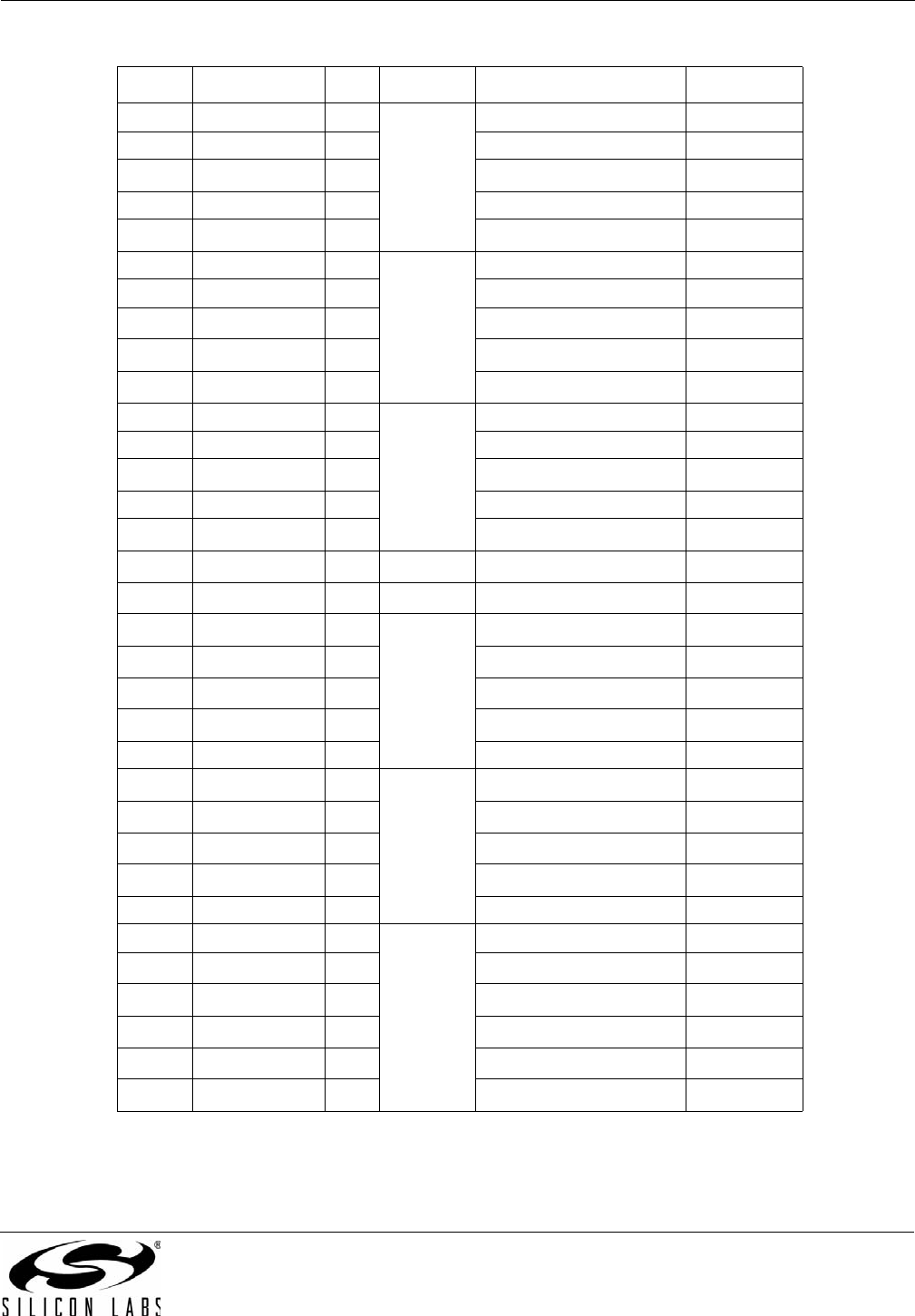

69 HLML 173.37 4/5 x 64/66 x 237/255 125

70 HLMM 64/66 x 237/255 156.25

71 HLMH

237/255 161.13

72 HLHL 4 x 237/255 644.53

73 MHMM

4693.48

74 HLHM 176.1 2/3 x 64/66 x 238/255 106.25

75 HLLL 64/66 x 238/255 159.375

76 HLLM

238/255 164.36

77 HLLH

4 x 238/255 657.42

78 MHMM

4704.38

79 HLHH 176.84 2/3 x 64/66 x 237/255 106.25

80 HLMM 64/66 x 237/255 159.375

81 HLMH

237/255 164.36

82 HLHL 4 x 237/255 657.42

83 MHMM

4707.35

84 HMLL

212.5 2 425

85 HMLM

425 1 425

86 HMLH

644.53 1/5 x 64/66 125

87 HMML

1/4 161.13

88 HMMM

1644.53

89 HMMH

255/238 690.57

90 HMHL 255/237 693.48

91 HMHM

657.42 1/6 x 64/66 106.25

92 HMML

1/4 164.36

93 HMMM

1657.42

94 HMMH

255/238 704.38

95 HMHL 255/237 707.35

96 HMHH 690.57 1/5 x 64/66 x 238/255 125

97 HHLL

1/4 x 64/66 x 238/255 156.25

98 HHLM

1/4 x 238/255 161.13

99 HMML

1/4 172.64

100 HHLH

238/255 644.53

101 HMMM

1690.57

Table 17. Datacom Clock Multiplication Settings (FRQTBL = M, CK_CONF = 0) (Continued)

Setting FRQSEL[3:0]

WB

f

IN

(MHz) Mult Factor f

OUT

* (MHz)