Si53xx-RM

Rev. 0.5 47

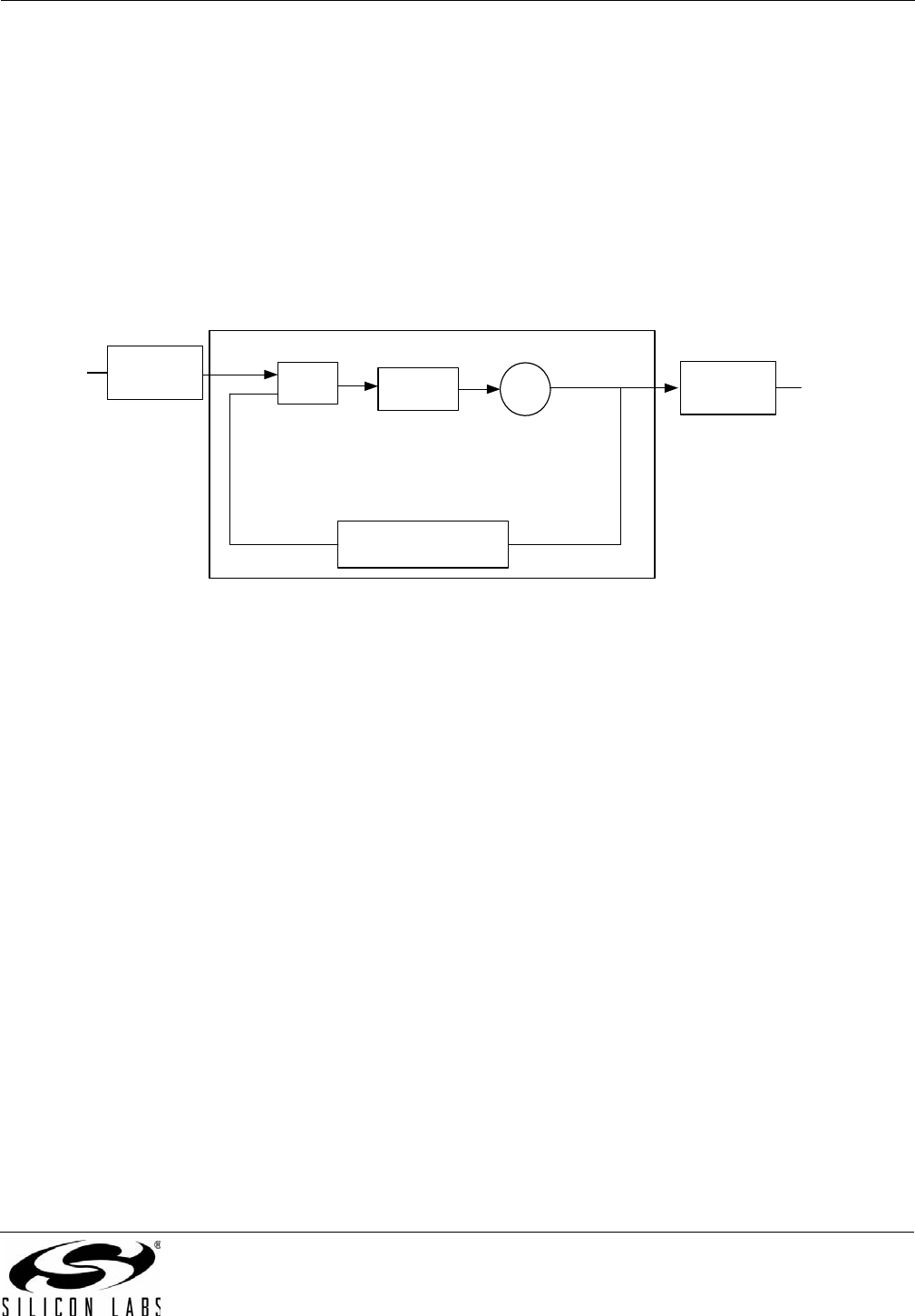

5.1. Clock Multiplication

Fundamental to these parts is a clock multiplication circuit that is simplified in Figure 21. By having a large range of

dividers and multipliers, nearly any output frequency can be created from a fixed input frequency. For typical

telecommunications and data communications applications, the hardware control parts (Si5316, Si5322, Si5323,

Si5365, and Si5366) provide simple pin control.

The microprocessor controlled parts (Si5319, Si5324, Si5325, Si5326, Si5327, Si5367, Si5368, and Si5369)

provide a programmable range of clock multiplications. To assist users in finding valid divider settings for a

particular input frequency and clock multiplication ratio, Silicon Laboratories offers PC-based software (DSPLLsim)

that calculates these settings automatically. When multiple divider combinations produce the same output

frequency, the software recommends the divider settings yielding the recommended settings for phase noise

performance and power consumption.

Figure 21. Clock Multiplication Circuit

Fin

DSPLL

Phase

Detector

Digital

DCO

Digital Loop

Filter

Divide By N2

Divide By N3

Divide By NC1

Fout

f

OUT

= (Fin/N3) x N2/NC1

f

vco

= (Fin/N3) x N2

f

3

f

VCO