Si53xx-RM

84 Rev. 0.5

7.4.2.2. Detailed Automatic Clock Selection Description (Si5367, Si5368, Si5369)

The prioritization of clock inputs for automatic switching is shown in Table 41. For example, if

CK_CONFIG_REG = 0 and the desired clock priority order is CKIN4, CKIN3, CKIN2, and then CKIN1 as the

lowest priority clock, the user should set CK_PRIOR1[1:0] = 11, CK_PRIOR2[1:0] = 10, CK_PRIOR3[1:0] = 01, and

CK_PRIOR4[1:0] = 00.

If CK_CONFIG_REG = 1 and the desired clock priority is CKIN1/CKIN3 and then CKIN2/CKIN4, the user should

set CK_PRIOR1[1:0] = 00 and CK_PRIOR2[1:0] = 01 (CK_PRIOR3[1:0] and CK_PRIOR4[1:0] are ignored in this

case).

The following discussion describes the clock selection algorithm for the case of four possible input clocks

(CK_CONFIG_REG = 0) in the default priority arrangement (priority order CKIN1, CKIN2, CKIN3, CKIN4).

Automatic switching mode selects CKIN1 at powerup, reset, or when in revertive mode with no alarms present on

CKIN1. If an alarm condition occurs on CKIN1 and there are no active alarms on CKIN2, the device switches to

CKIN2. If both CKIN1 and CKIN2 are alarmed and there is no alarm on CKIN3, the device switches to CKIN3. If

CKIN1, CKIN2, and CKIN3 are alarmed and there is no alarm on CKIN4, the device switches to CKIN4. If alarms

exist on CKIN1, CKIN2, CKIN3, and CKIN4, the device enters digital hold mode. If automatic mode is selected and

the frequency offset alarms (FOS1_INT, FOS2_INT, FOS3_INT, FOS4_INT) are disabled, automatic switching is

not initiated in response to FOS alarms. The loss-of-signal alarms (LOS1_INT, LOS2_INT, LOS3_INT, LOS4_INT)

are always used in making automatic clock selection choices. In non-revertive mode, once CKIN2 is selected,

CKIN2 selection remains as long as it is valid even if alarms are cleared on CKIN1.

7.4.3. Hitless Switching with Phase Build-Out (Si5324, Si5326, Si5327, Si5368, Si5369, Si5374)

Silicon Laboratories switching technology performs phase build-out, which maintains the phase of the output when

the input clock is switched. This minimizes the propagation of phase transients to the clock outputs during input

clock switching. All switching between input clocks occurs within the input multiplexer and phase detector circuitry.

The phase detector circuitry continually monitors the phase difference between each input clock and the DSPLL

output clock, f

OSC

. The phase detector circuitry can lock to a clock signal at a specified phase offset relative to f

OSC

so that the phase offset is maintained by the PLL circuitry.

At the time a clock switch occurs, the phase detector circuitry knows both the input-to-output phase relationship for

the original input clock and for the new input clock. The phase detector circuitry locks to the new input clock at the

new clock's phase offset so that the phase of the output clock is not disturbed. The phase difference between the

two input clocks is absorbed in the phase detector's offset value, rather than being propagated to the clock output.

The switching technology virtually eliminates the output clock phase transients traditionally associated with clock

rearrangement (input clock switching).

Note that hitless switching between input clocks applies only when the input clock validation time is

VALTIME[1:0] = 01 or higher.

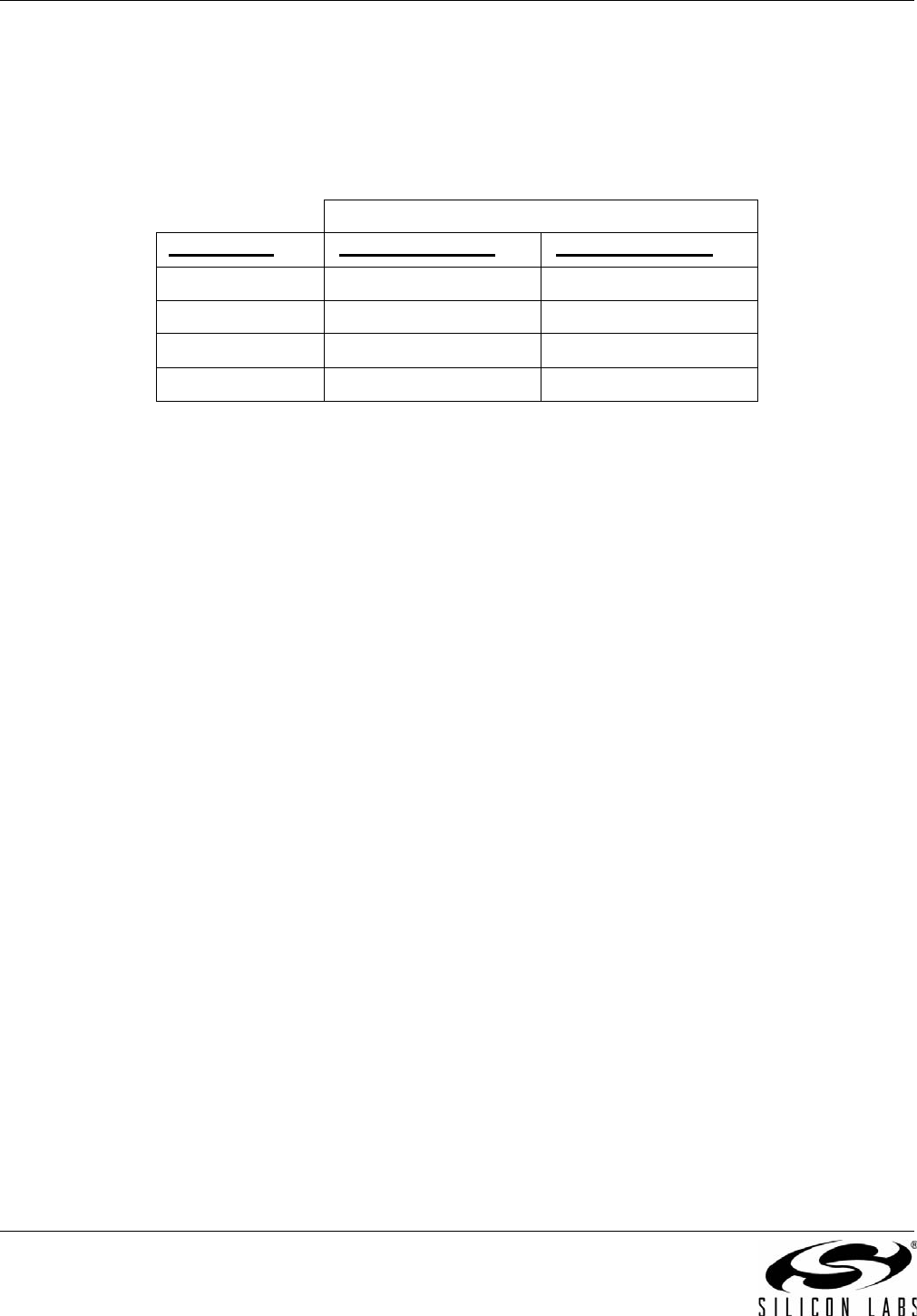

Table 41. Input Clock Priority for Auto Switching

Selected Clock

CK_PRIORn

[1:0] CK_CONFIG_REG = 0 CK_CONFIG_REG = 1

00 CKIN1 CKIN1/CKIN3

01 CKIN2 CKIN2/CKIN4

10 CKIN3 Not Used

11 CKIN4 Not Used