ARM720T_LH79520 – Sharp LH79520 SoC with ARM720T 32-bit RISC Processor

Design Featuring an OpenBus System

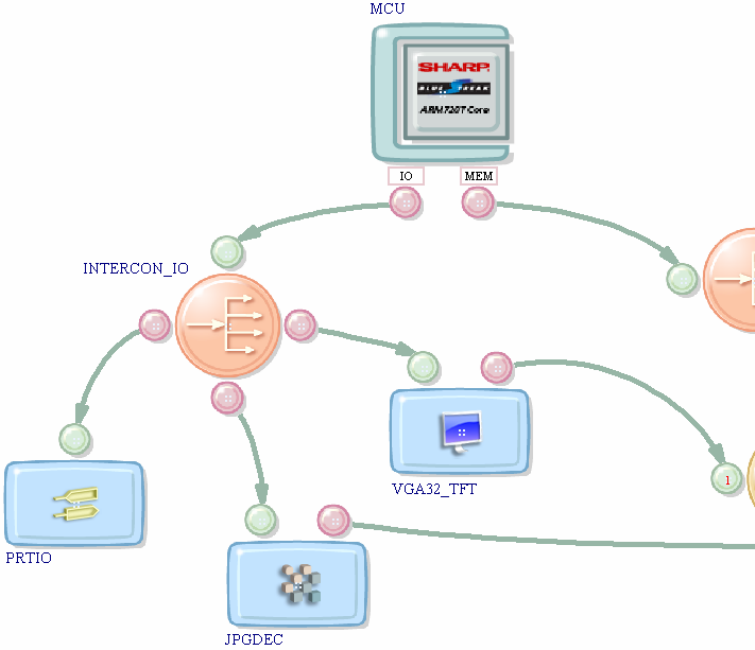

Figure 11 illustrates identical use of the ARM720T_LH79520 within a design where the main processor system has been

defined as an OpenBus System. Peripherals (and memory) are connected to the processor through an Interconnect component.

The OpenBus System environment is a much more abstract and intuitive place to create a design, where the interfaces are

reduced to single ports and connection is made courtesy of single links.

Figure 11. Wiring up the ARM720T_LH79520 wrapper as part of an OpenBus System.

Much of the configuration is handled for you, with each peripheral added as a slave to the Interconnect component by virtue of

its link. The Interconnect contains information regarding each peripheral's address bus size and a default decoder address width.

All that is really needed is specification of the base address for each peripheral – where in the ARM720T_LH79520's address

space these devices are to be mapped.

An OpenBus System is defined on an OpenBus System Document (

*.OpenBus). This document is referenced from the FPGA

design's top-level schematic sheet through a sheet symbol. Figure 12 illustrates the interface circuitry between the

ARM720T_LH79520's physical processor interface and the physical pins of the target FPGA device – represented by the

PROCESSOR_ARM7_LH79520 port component.

CR0162 (v2.0) March 10, 2008 21