Rev. 01-12-07 Page 4 SMSC LPC47M997

PRODUCT PREVIEW

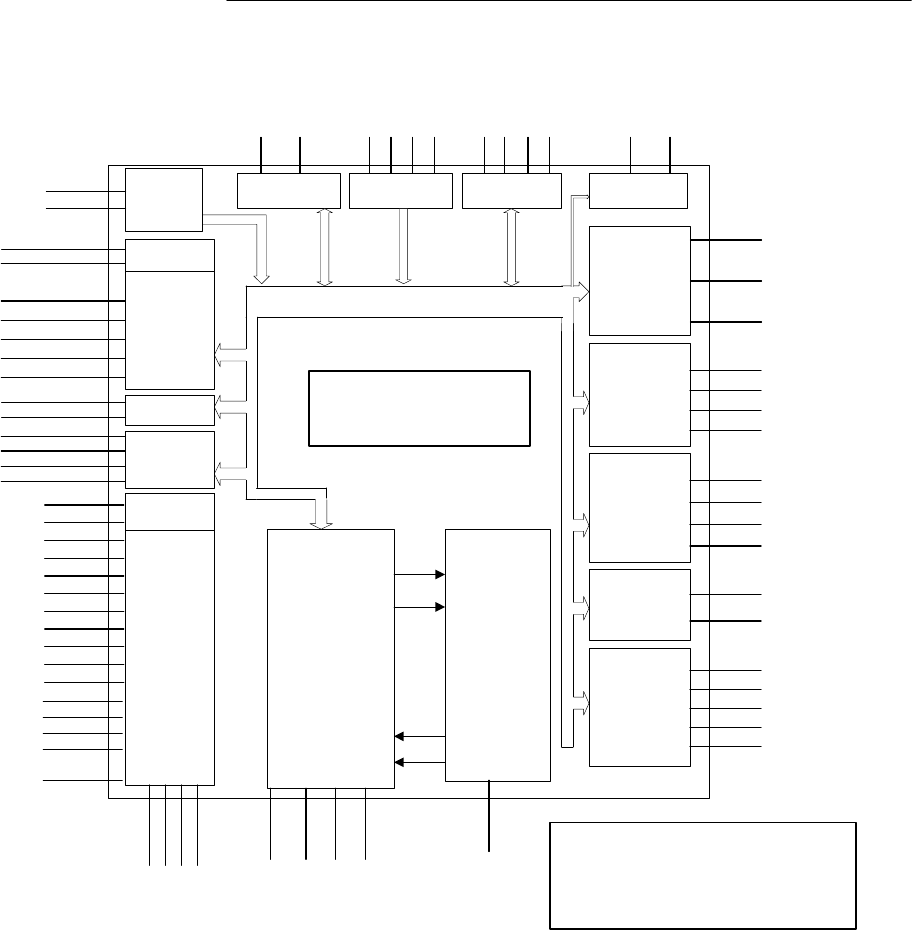

Block Diagram

FAN2*

J1X, J1Y*

IRTX2*

IRRX2*

LPC47M997

(128 QFP)

DIGITAL DATA

SEPARATOR

WITH WRITE

PRECOM-

PENSATION

SMC PROPRIETARY

82077 COMPATIBLE

VERTICAL

FLOPPYDISK

CONTROLLER CORE

WDATA

WCLOCK

RCLOCK

RDATA

Game Port Fan Control2nd Infrared Port

Multi-Mode

Parallel Port

with

ChiProtect

TM

/

FDC MUX

(see LPC47B27x)

PD[7,0]

Busy, Slct, PE,

ERROR, ACK

STROBE, INIT, SLCTIN,

ALF

FAN_TACH2*

FAN_TACH1*

FAN1*

J2B1, J2B2*

J1B1, J1B2*

J2X, J2Y*

LEDs

LED2*

LED1*

Internal Bus

(Data, Address, and Control lines)

High-Speed

16550A

UART

PORT 1

TXD1, RXD1

DSR1, DTR1

DCD1, RI1

CTS1, RTS1

MPU-401

Serial Port

MIDI_OUT*

MIDI_IN*

Keyboard/Mouse

8042

controller

KCLK, MCLK

KDATA, MDATA

GateA20*

KRESET*

P12*, P16*, P17*

High-Speed

16550A

UART

PORT 2

TXD2 (IRTX)*,

RXD2 (IRRX)*

DSR2*, DTR2*

DCD2*, RI2*

CTS2*, RTS2 *

Power Mgmt

IO_PME*

IO_SMI*

General

Purpose

I/O

GP1[0:7]*

GP2[0:2,4:7]*

GP3[0:7]*, GP4[0:3]*

GP5[0:7]*, GP6[0:1]*

RDATA, WDATA

DIR, STEP,

DSKCHG, DS0, DS1*

MTR0, MTR1*,TRK0,

INDEX, WRTPRT

DRVDEN0*, DRVDEN1*

WGATE, HDSEL

Note 1: This diagram does not show power and ground

connections.

Note 2: Functions with "*" are located on multifunctional pins.

This diagram is designed to show the various functions

available on the chip (not pin layout).

Hardware

Monitoring

SMBus

CLOCK

GEN

CLK32

CLOCKI

LAD[3:0]

LFrame

LDRQ

PCI_RESET

LPCPD

SER_IRQ

PCI_CLK

LPC

Bus Interface

SERIAL

IRQ

A0/RESET#/THERM#/

XNOR_OUT

Vccp_IN

+3.3V_IN

+2.5V_IN

SDA

SCL

VID0

VID1

VID2

VID3

12V_IN/VID4

+5V_IN

HVSS

HVCC

+1.8V_IN

+1.5V_IN

D1+

D1-

D0+

D0-

Figure 1 - LPC47M997 Block Diagram