Hi-Speed USB Transceiver with 1.8V ULPI Interface - Multi-Frequency Reference Clock

Revision 1.11 (10-31-08) 8 SMSC USB3310 REV C

PRODUCT PREVIEW

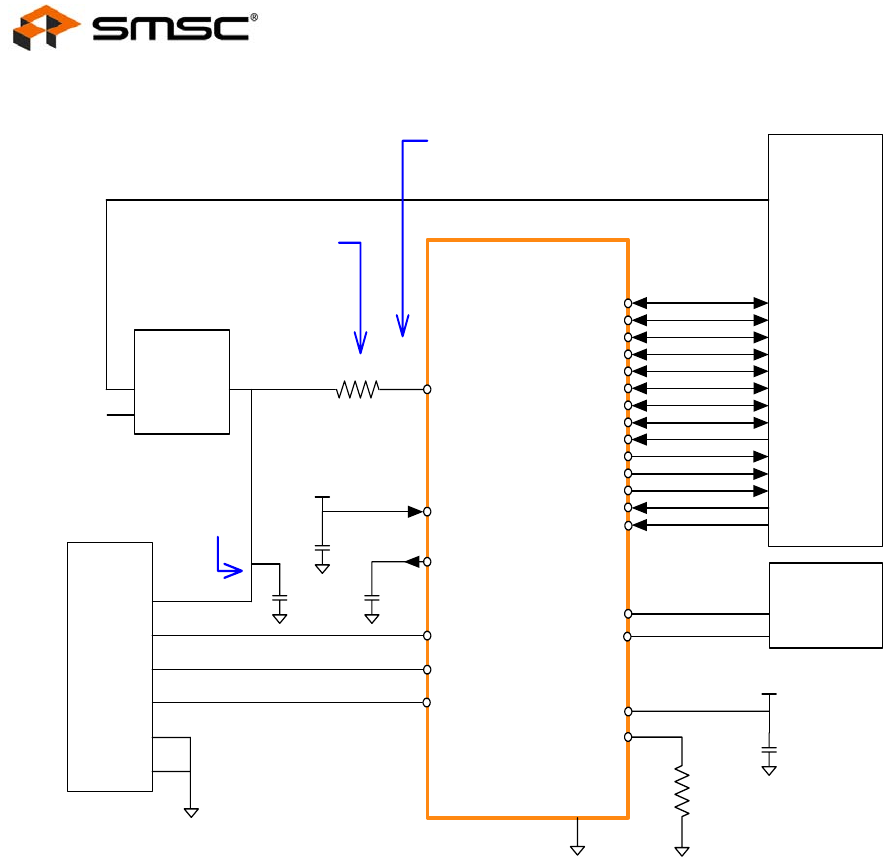

Figure 4 USB3310 QFN Application Diagram (Host or OTG)

Link Controller

USB331X

RBIAS

DIR

NXT

STP

CLKOUT

DATA7

DATA6

DATA5

DATA4

DATA3

DATA2

DATA0

DATA1

REFCLK

VBAT

VDD3.3

VBUS

DM

DP

RESETB

USB

Receptacle

DM

DP

DIR

NXT

STP

CLKOUT

DATA7

DATA6

DATA5

DATA4

DATA3

DATA2

DATA0

DATA1

RESETB

6

5

24

1

GND FLAG

2

3

VBUS

GND

SHIELD

C

VBUS

4

3

2

VBUS Switch

OUT

EN

C

OUT

C

BYP

IN

ID

4

ID

1

3.1 - 5.5V

Supply

8.06k

Reference

5V

R

VBUS

The capacitor C

VBUS

must be

installed on this side of R

VBUS

.

Signal at REFCLK

must comply with

V

IH

and V

IL

VDD18

21

C

BYP

1.8V Supply

REFSEL[1]

14

REFSEL[0]

15

Pin Strap

Determines

REFCLK

frequency

CPEN

Voltage at the VBUS pin must not be allowed

to exceed V

VMAX

.

R

VBUS

may be installed in this

configuration to assist in protecting

the VBUS pin. 820 Ohms will

protect against VBUS transients up

to 8.5V.

7

8

9

10

12

13

16

17

20

18

19

11

22

23