High Speed Inter-Chip USB 2.0 Hub and Flash Media Controller

Datasheet

SMSC USB4640/USB4640i 7 Revision 1.0 (06-01-09)

DATASHEET

Chapter 1 Overview

The SMSC USB4640/USB4640i is a Hi-Speed HSIC USB hub and card reader combo solution with

an upstream port compliant to HSIC 1.0, a supplement to the USB 2.0 specification. The two

downstream ports are compliant with the USB 2.0 specification. In addition, The dedicated flash

media reader/writer is internally attached to a 3rd downstream port of the hub as a USB Compound

device.

High Speed Inter-Chip (HSIC) is a digital interconnect bus that enables the use of USB technology

as a low-power chip-to-chip interconnect at speeds up to 480 Mb/s. Please refer to the “High-Speed

Inter-Chip USB Electrical Specification Revision 1.0 as of September 23, 2007” which can be found

at http://www.usb.org/developers/docs/docs. This combo solution supports today’s popular multi-

format flash media cards. This multi-format flash media controller and USB hub combo features two

exposed downstream USB ports available for external peripheral expansion.

The USB4640/USB4640i will attach to an upstream port as a Full-Speed hub or as a Full-/Hi-Speed

hub. The hub supports Low-Speed, Full-Speed, and Hi-Speed (if operating as a Hi-Speed hub)

downstream devices on all of the enabled downstream ports.

All required resistors on the USB ports are integrated into the hub. This includes all series

termination resistors on D+ and D– pins and all required pull-down and pull-up resistors. The over-

current sense inputs for the downstream facing ports have internal pull-up resistors.

The USB4640/USB4640i includes programmable features such as:

PortMap which provides flexible port mapping and disable sequences. The downstream ports of a

USB4640/USB4640i hub can be reordered or disabled in any sequence to support multiple platform

designs with minimum effort. For any port that is disabled, the USB4640/USB4640i automatically

reorders the remaining ports to match the USB host controller’s port numbering scheme.

PortSwap which adds per-port programmability to USB differential-

pair pin locations. PortSwap allows direct alignment of USB signals

(D+/D-) to connectors avoiding uneven trace length or crossing of

the USB differential signals on the PCB.

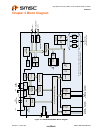

PHYBoost which enables four programmable levels of USB signal

drive strengths in downstream port transceivers. PHYBoost attempts

to restore USB signal integrity. The diagram on the right shows an

example of Hi-Speed USB eye diagrams before (PHYBoost at 0%)

and after (PHYBoost at 12%) signal integrity restoration in a

compromised system environment.