3.22HCPort1StatusandControlRegister(HCRHPORTSTATUS1)

Registers

www.ti.com

TheHCport1statusandcontrolregister(HCRHPORTSTATUS1)reportsandcontrolsthestateofUSB

hostport1.HCRHPORTSTATUS1isshowninFigure23anddescribedinTable23.

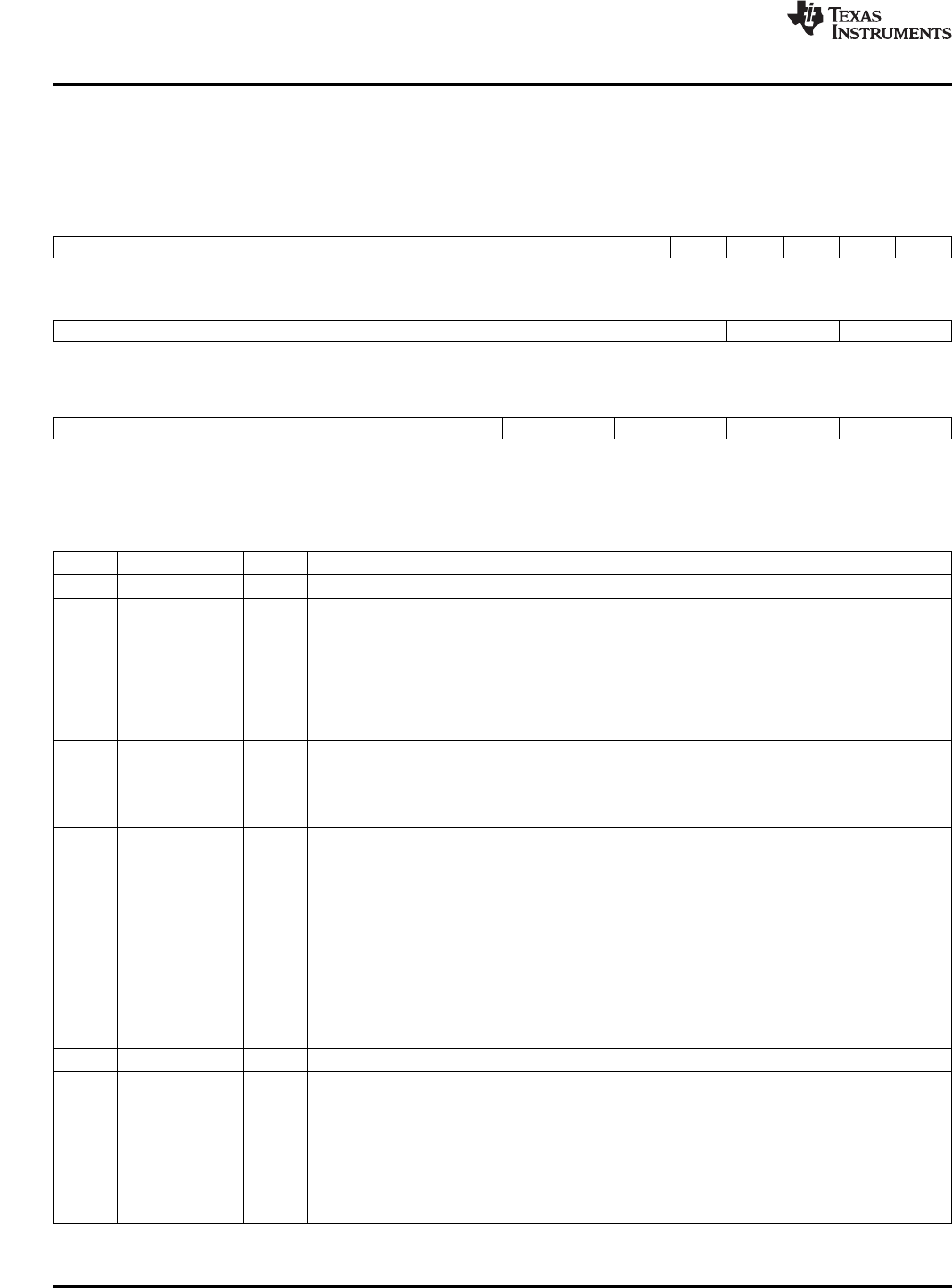

Figure23.HCPort1StatusandControlRegister(HCRHPORTSTATUS1)

31212019181716

ReservedPRSCOCICPSSCPESCCSC

R-0R/W1C-0R/W-0R/W1C-0R/W1C-0R/W1C-0

151098

ReservedLSDA/CPPPPS/SPP

R-0R/W-0R/W-1

7543210

ReservedPRS/SPRPOCI/CSSPSS/SPSPES/SPECCS/CPE

R-0R/W-0R/W-0R/W-0R/W-0R/W-0

LEGEND:R/W=Read/Write;R=Readonly;W1C=Write1toclear(writing0hasnoeffect);-n=valueafterreset

Table23.HCPort1StatusandControlRegister(HCRHPORTSTATUS1)FieldDescriptions

BitFieldValueDescription

31-21Reserved0Reserved

20PRSCPort1resetstatuschange.Awriteof1clearsthisbit;awriteof0hasnoeffect.

0Port1portresetstatusbithasnotchanged.

1Port1portresetstatusbithaschanged.

19OCIC0Port1overcurrentindicatorchange.Becausethedevicedoesnotprovideinputsforsignaling

externalovercurrentindicationtotheUSBhostcontroller,thisbitisalways0.Overcurrent

monitoring,ifrequired,mustbehandledthroughsomeothermechanism.Thisbithasno

relationshiptotheOTGcontrollerregisterbitsthatrelatetoVBUS.

18PSSCPort1suspendstatuschange.Awriteof1clearsthisbit;awriteof0hasnoeffect.

0Port1portsuspendstatushasnotchanged.

1Port1portsuspendstatushaschanged.Suspendstatusisconsideredtohavechangedonlyafter

theresumepulse,low-speedEOP,and3-mssynchronizationdelayshavebeencompleted.

17PESCPort1enablestatuschange.Awriteof1clearsthisbit;awriteof0hasnoeffect.

0Port1portenablestatushasnotchanged.

1Port1portenablestatushaschanged.

16CSCPort1connectstatuschange.IftheDR[1]bitintheHCroothubBregister(HCRHDESCRIPTORB)

issetto1toindicateanonremovableUSBdeviceonport1,thisbitissetonlyafteraroothub

resettoinformthesystemthatthedeviceisattached.Awriteof1clearsthisbit;awriteof0hasno

effect.

0Port1currentconnectstatushasnotchanged.

1Port1currentconnectstatushaschangedduetoaconnectordisconnectevent.Ifcurrentconnect

statusis0whenasetportreset,setportenable,orsetportsuspendwriteoccurs,thenthisbitis

set.

15-10Reserved0Reserved

9LSDA/CPPPort1low-speeddeviceattached/clearportpower.Thisbitisvalidonlywhenport1current

connectstatusis1.Thehostcontrollerdrivercanwritea1tothisbittocleartheport1portpower

statusbit;awriteof0hasnoeffect.TheUSBhostcontrollerdoesnotcontrolexternalportpower

usingOHCImechanisms,so,ifrequired,USBhostportpowermustbecontrolledthroughother

means.ThisbithasnorelationshiptotheOTGcontrollerregisterbitsthatrelatetoVBUS.System

softwarecanupdatethisregistertosimplifyhostcontrollerdriverand/orOTGdrivercoding.

0Full-speeddeviceisattachedtoport1.

1Low-speeddeviceisattachedtoport1.

30UniversalSerialBusOHCIHostControllerSPRUFM8–September2008

SubmitDocumentationFeedback