YMF724F

September 21, 1998

-10-

1-2. PCI Configuration Register

In addition to the Configuration Register defined by PCI Revision 2.1, DS-1 provides proprietary PCI

Configuration Registers in order to control legacy audio function, such as OPL3, Sound Blaster Pro, MPU401

and Joystick. These additional registers are configured by BIOS or the configuration software from

YAMAHA Corporation.

The following shows the overview of the PCI Configuration Register.

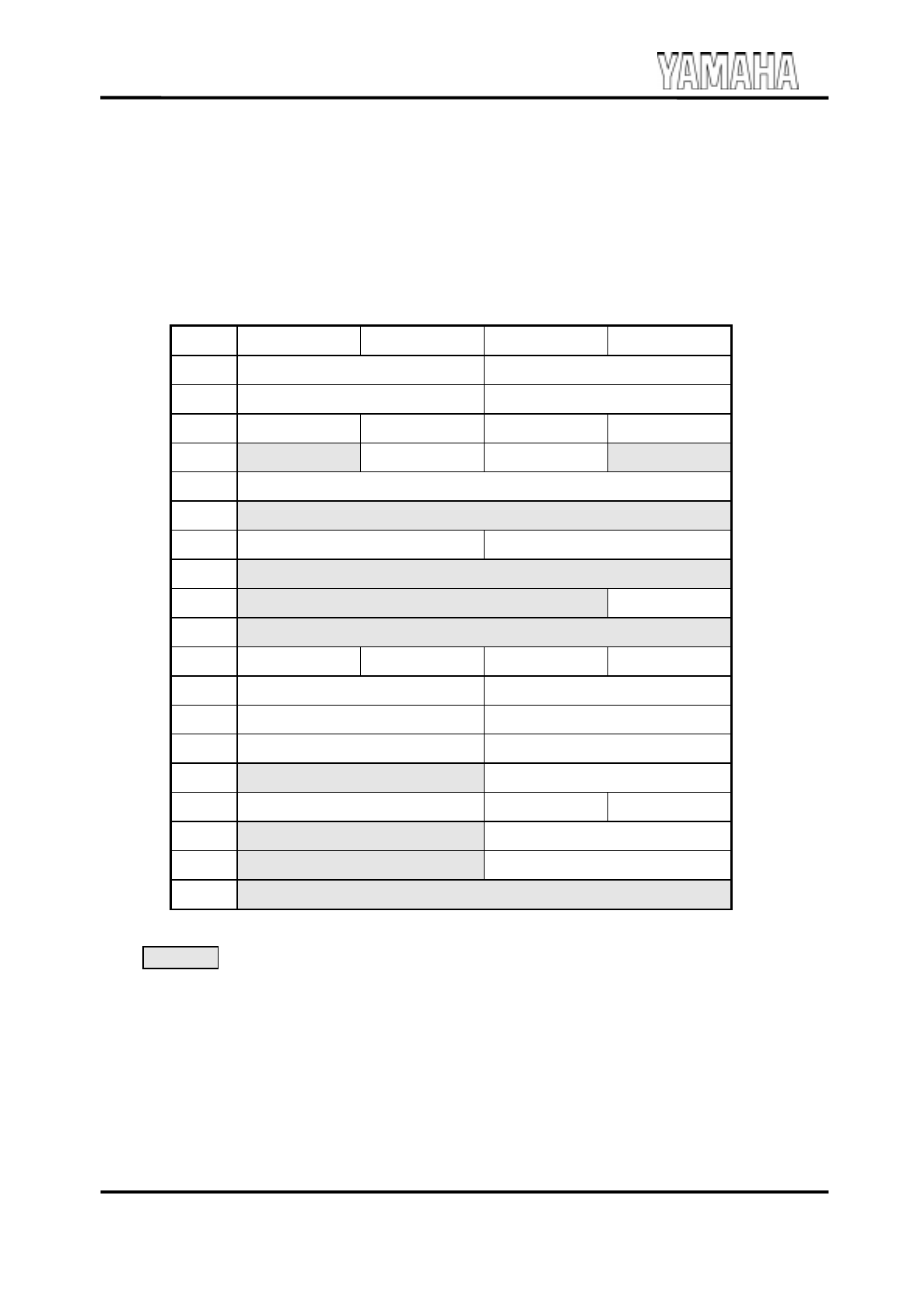

Offset b[31..24] b[23..16] b[15..8] b[7..0]

00-03h Device ID Vendor ID

04-07h Status Command

08-0Bh Base Class Code Sub Class Code Programming IF Revision ID

0C-0Fh Reserved Header Type Latency Timer Reserved

10-13h PCI Audio Memory Base Address

14-2Bh Reserved

2C-2Fh Subsystem ID Subsystem Vendor ID

30-33h Reserved

34-37h Reserved Cap Pointer

38-3Bh Reserved

3C-3Fh Maximum Latency Minimum Grant Interrupt Pin Interrupt Line

40-43h Extended Legacy Audio Control Legacy Audio Control

44-47h Subsystem ID Write Subsystem Vendor ID Write

48-4Bh DS-1 Power Control DS-1 Control

4C-4Fh Reserved D-DMA Slave Configuration

50-53h Power Management Capabilities Next Item Pointer Capability ID

54-57h Reserved Power Management Control / Status

58-5Bh Reserved ACPI Mode

5C-FFh Reserved

Reserved registers are hardwired to “0”. All data written to these registers are discarded. The values

read from these registers are all zero.

DS-1 can be accessed by using any bus width, 8-bit, 16-bit or 32-bit.