Your ePlatform Partner

User’s Manual for Advantech SOM-A2552 series module V1.00

19

2 2.

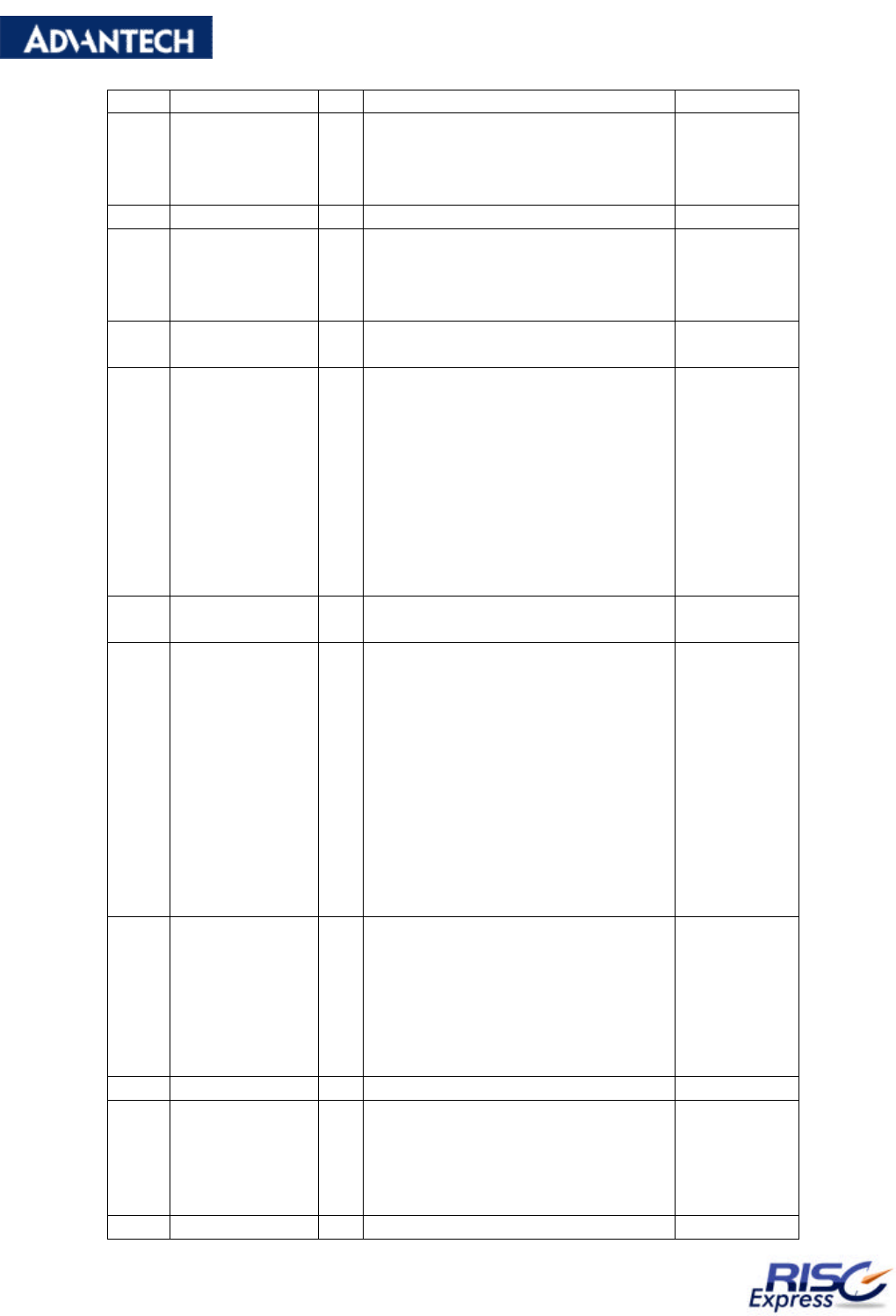

79 nSA_SKT0_IOI

S16

I IO Select 16. (input) Acknowledge

from the PCMCIA card that the

current address is a valid 16 bit

wide I/O address.

Pull high with

10Kohm

80 SA_SKT0_VCC

P PCMCIA/CF slot 0 power pin. Powered

81 nSA_SKT1_IOI

S16

I PCMCIA/CF slot 0 IO Select 16.

Acknowledge from the PCMCIA

card that the current address is a

valid 16 bit wide I/O address.

Pull high with

10Kohm

82 nSA_PWR_ON

I

System suspend/wakeup input pin.

Falling edge triggered.

Pull high with

10Kohm

83 nBATT_FALT

I Main Battery Fault. Signals that

main battery is low or removed.

Assertion causes PXA255

processor to enter sleep mode or

force an Imprecise Data Exc

eption,

which cannot be masked. PXA255

processor will not recognize a

wakeup event while this signal is

asserted. Minimum assertion time

for nBATT_FAULT is 1 ms.

Pull high with

100Kohm

84 nSW_RESET

I System software reset input pin.

Falling edge triggered.

Pull high with

10Kohm

85 nVDD_FALT I VDD Fault. Signals that the main

power source is going out of

regulation. nVDD_FAULT causes

the PXA255 processor to enter

sleep mode or force an Imprecise

Data Exception, which cannot be

masked. nVDD_FAULT is ignored

after a wakeup event until the

power supply timer completes

(approximately 10 ms). Minimum

assertion time for nVDD_FAULT is

1 ms.

Pull high with

100Kohm

86 nRESET_OUT

O

Reset Out. Asserted when

nRESET is asserted and deasserts

after nRESET is deasserted but

before the first instruction fetch.

nRESET_OUT is also asserted for

“soft” reset events: sleep,

watchdog reset, or GPIO reset.

No pulling

87 GND P Ground -

88 PWR_EN

O

Power Enable for the power

supply. (output) When negated, it

signals the power supply to

remove power to the core because

the system is entering sleep mode.

Pull high with

100Kohm

89 BAT_VCC P 3.0V li-

ion coin battery positive

No pulling