Your ePlatform Partner

User’s Manual for Advantech SOM-A2552 series module V1.00

29

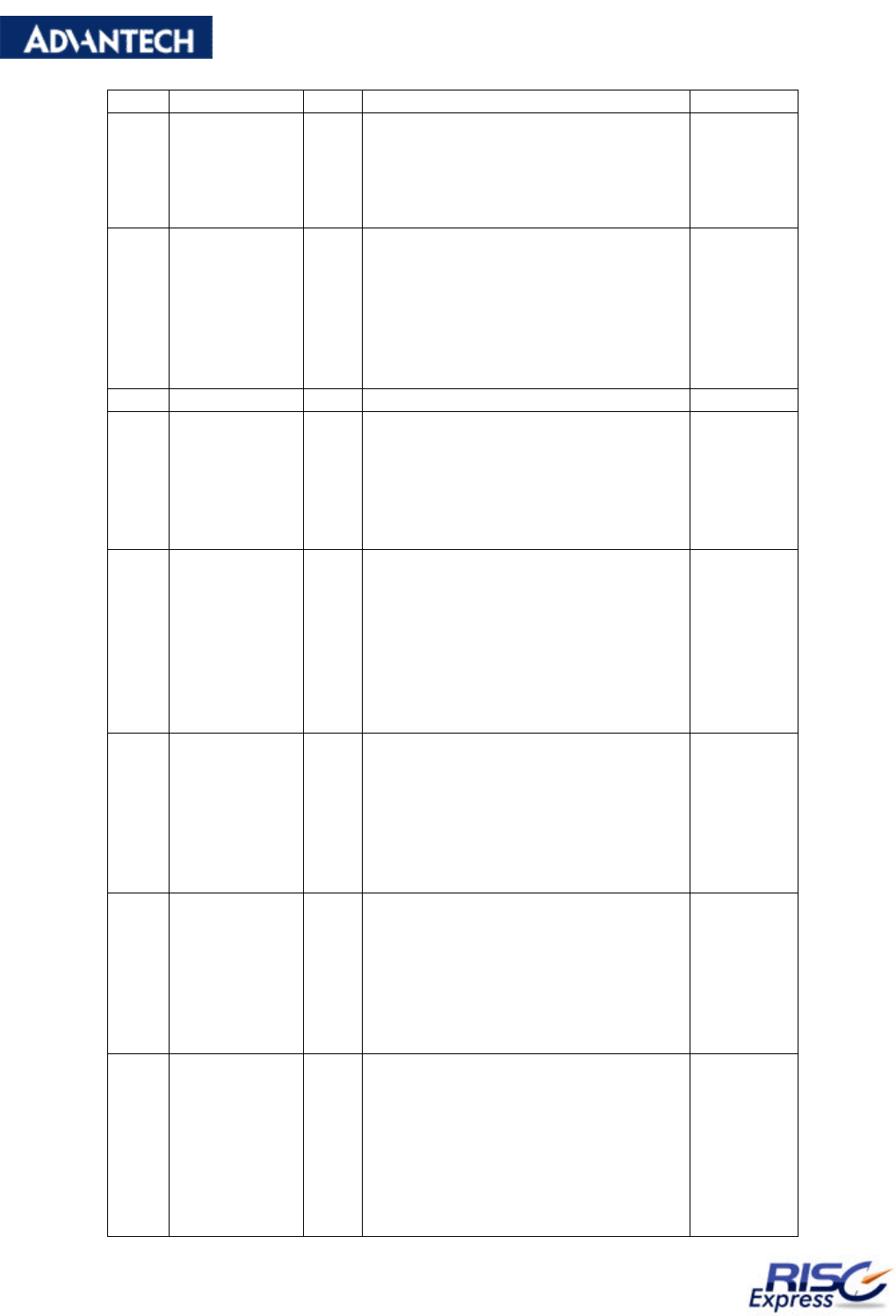

address.

B40

nBUF_PWE O

PCMCIA write enable.

Performs

writes to PCMCIA memory and to

PCMCIA attribute space. Also used

as the write enable signal for

Variable Latency I/O.

No pulling

A40

KEYPAD_IRQ

I

GPIO pin. Advantech default

function is used as matrix Keypad

IRQ. The pin directly connects to

PXA255 GPIO2 (L13 pin). If user

doesn’t use the matrix key pad

function, use can use this pin as

GPIO pin.

No pulling

B41

N.C. - N.C. just float this pin. -

A41

PXA_GP7 IO

GPIO pin. The pin directly connects

to PXA255 GPIO7 (G15 pin). This

GPIO pin is available for user to use.

No pulling

(For

SOM-

255F

is

PXA_GPIO

7)

B42

EVA_IRQ -

Advantech use this pin to control

companion

chip as IRQ function.

The pin is not available for CSB

design of SOM-

A2558 &

SOM-A255F platform. SOM-

A2558

& SOM-

A255F user must float this

pin. This pin is directly connected to

SoC PXA255 GPIO9(F12).

-

A42

C950_485_IR

Q

I

Advantech default function is u

sed

as external 16C950 solution IC IRQ.

The pin directly connects to PXA255

GPIO10 (F7 pin). If user doesn’t

design 16C950 on CSB to expand

COM function, user could use this

pin as GPIO.

No pulling

B43

LAN1_IRQ I

Advantech default function is used

as exte

rnal LAN solution IC IRQ. The

pin directly connects to PXA255

GPIO17 (D12 pin). If user doesn’t

design the other LAN chip on CSB to

expand LAN function, user could use

this pin as GPIO.

No pulling

A43

USB_IRQ I

Advantech default function is used

as extern

al USB host solution IC

IRQ. The pin directly connects to

PXA255 GPIO27 (B9 pin). If user

doesn’t design the other USB

solution chip on CSB to expand USB

host function, user could use this pin

as GPIO.

No pulling