138 Chapter 4

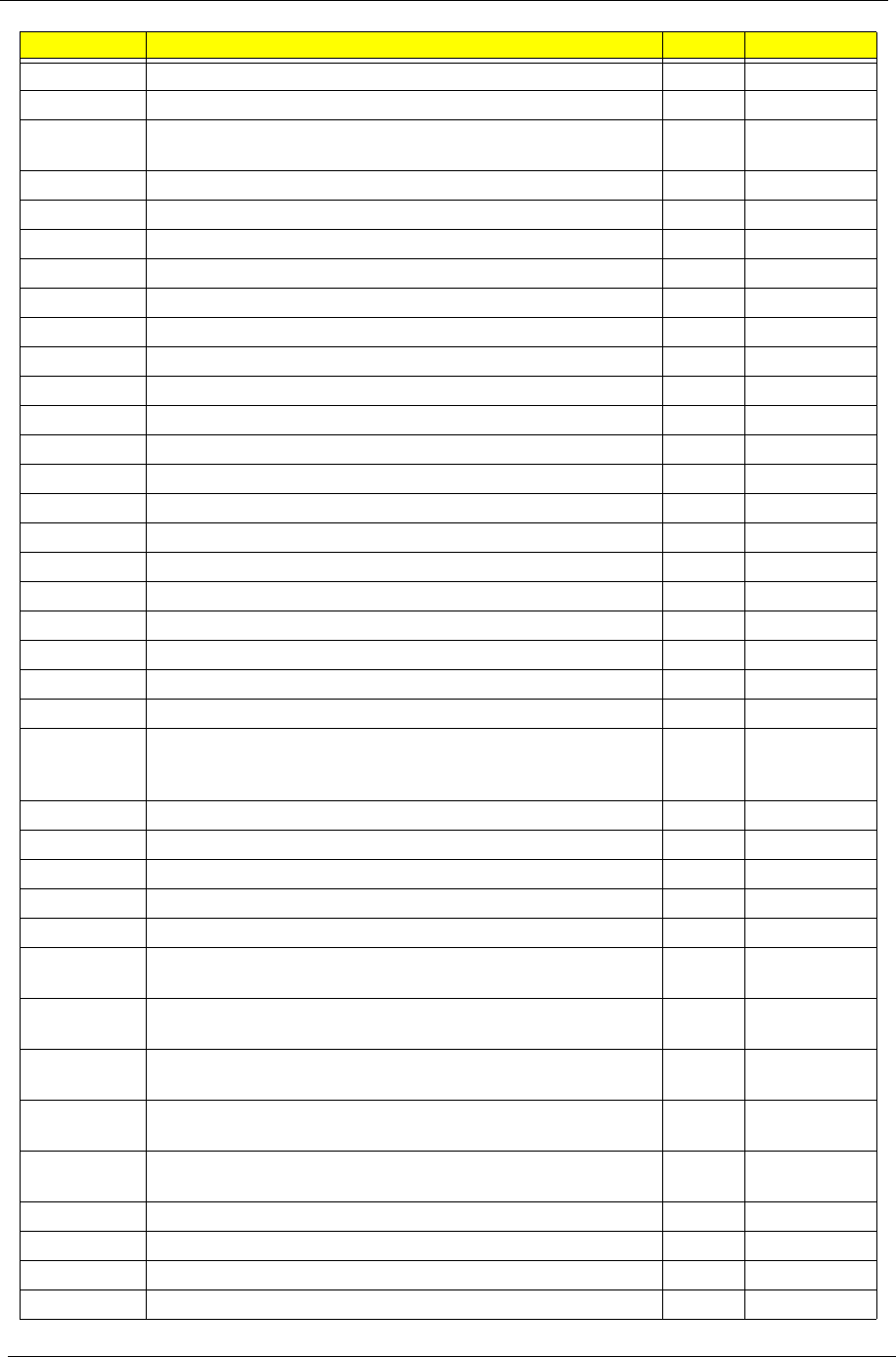

0x36 Setup DRAM control register for normal operation and enable PEI chipset/MRC

0x37 Do ZQ calibration for DDR3 PEI chipset/MRC

0x38 Perform final Dra/Drb programming, Set the mode of operation

for the memory channels

PEI chipset/MRC

0x39 Set Enhanced addressing mode for each channel PEI chipset/MRC

0x40 Perform steps required after JEDEC init PEI chipset/MRC

0x41 Program the receive enable reference timing control register PEI chipset/MRC

0x42 Post receive enable initialization PEI chipset/MRC

0x43 Enable sense amps. Reset read/write DQS pointers PEI chipset/MRC

0x44 Perform ME steps PEI chipset/MRC

0x45 Clear DRAM initialization bit in the ICH. PEI chipset/MRC

0x46 Program Thermal Management PEI chipset/MRC

0x47 Program TS on DIMM PEI chipset/MRC

0x48 Program TS on Board PEI chipset/MRC

0xAF Exit MRC PEI chipset/MRC

0xE0 #define MEM_ERR_BAD_DIMM (S11) PEI chipset/MRC

0xE1 #define MEM_ERR_ECC_DIMM (S06) PEI chipset/MRC

0xE2 #define MEM_ERR_SIDES (S07) PEI chipset/MRC

0xE3 #define MEM_ERR_WIDTH (S08, S10) PEI chipset/MRC

0xE4 #define MEM_ERR_TRFC (FindTrasTrpTrcd) PEI chipset/MRC

0xE5 #define MEM_ERR_CAS_LATENCY (S12, S13) PEI chipset/MRC

0xE6 #define MEM_ERR_REFRESH (ProgDrt) PEI chipset/MRC

0xE7 #define MEM_ERR_BL8 (S14) PEI chipset/MRC

0xE9 #define MEM_ERR_FREQUENCY (findTCLTacTClk, S13,

S12, ProgramGraphicsFrequency, ProgMchOdt,

GetPlatformData)

PEI chipset/MRC

0xEA #define MEM_ERR_SIZE (S14) PEI chipset/MRC

0xEC #define MEM_ERR_TRAS (FindTrasTrpTrcd) PEI chipset/MRC

0xED #define MEM_ERR_TRP (FindTrasTrpTrcd) PEI chipset/MRC

0xEE #define MEM_ERR_TRCD (FindTrasTrpTrcd) PEI chipset/MRC

0xEF #define MEM_ERR_TWR (FindTrasTrpTrcd) PEI chipset/MRC

0xF0 #define MEM_ERR_RCVEN_FINDLOW

(CalibrateRcvenForGroup)

PEI chipset/MRC

0xF1 #define MEM_ERR_RCVEN_FINDEDGE

(CalibrateRcvenForGroup)

PEI chipset/MRC

0xF2 #define MEM_ERR_RCVEN_FINDPREAMBLE

(CalibrateRcvenForGroup)

PEI chipset/MRC

0xF6 #define MEM_ERR_RCVEN_PREAMBLEEDGE

(CalibrateRcvenForGroup)

PEI chipset/MRC

0xF3 #define MEM_ERR_RCVEN_FINDCENTER

(CalibrateRcvenForGroup)

PEI chipset/MRC

0xF4 #define MEM_ERR_TYPE (S11, S04) PEI chipset/MRC

0xF5 #define MEM_ERR_RAWCARD (S11) PEI chipset/MRC

0xFA #define MEM_ERR_SFF (ProgWrioDll) PEI chipset/MRC

0xFB #define MEM_ERR_THERMAL (ProgramThrottling) PEI chipset/MRC

POST Code Function Phase Component