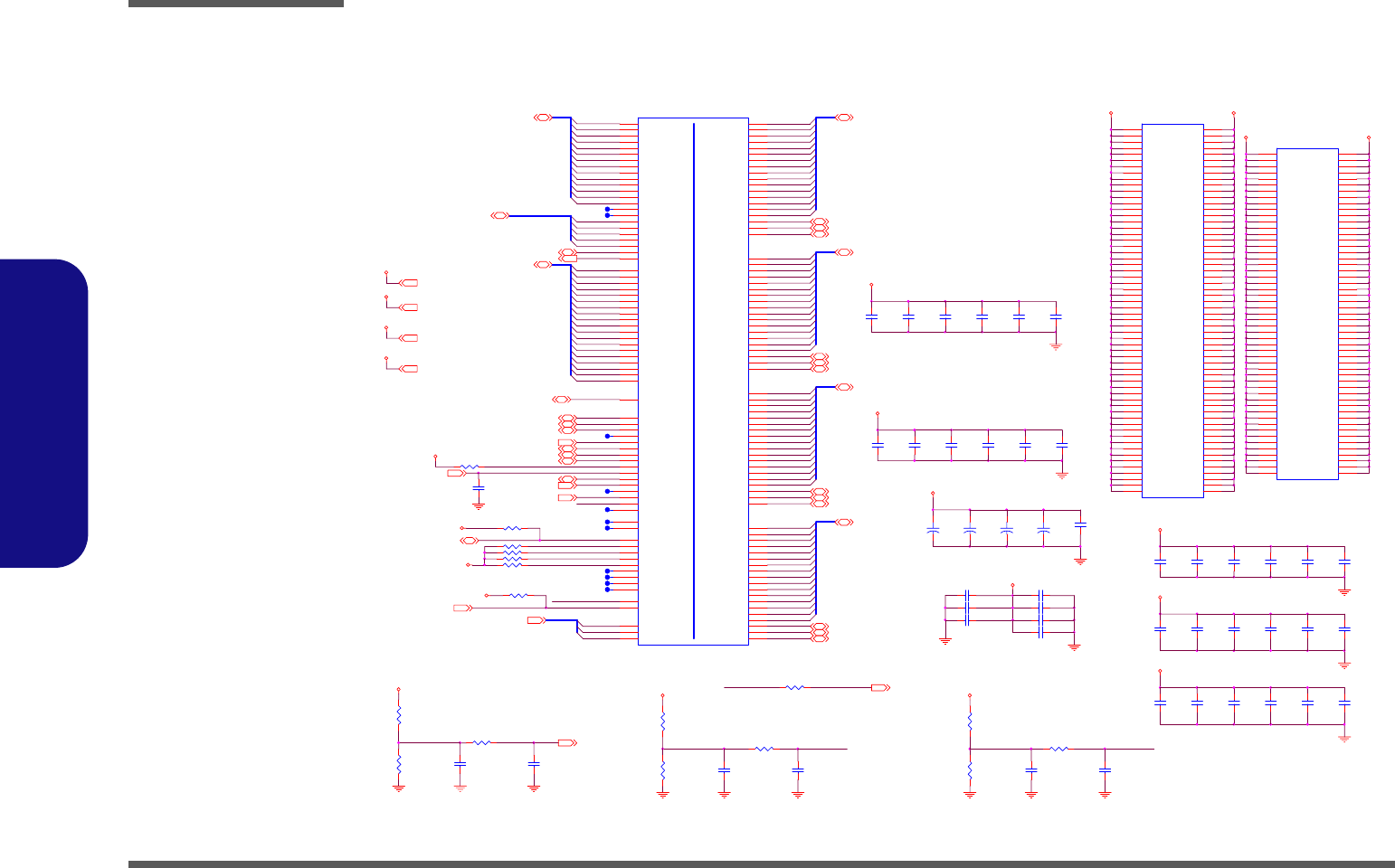

Schematic Diagrams

B - 4 CPU-1

B.Schematic Diagrams

CPU-1

VCORE

C123

33P _04

PLEASE COLSE TO Pin-H1

CPU_D#27

C 45 .1U _X7R _04

C488

10U /10V _08

C485

10U /10V _08

CPU_D#25

CPU_DEFER#5

PECI

CPU_D#23

CPU_D#53

C92

.1U_X7R_04

CPU_DSTBP0# 5

CPU_D#15

CPU_D#31

CPU_A#33

C492

10U /10V _08

CPU_BPRI#5

CPU_A#8

R47

210_ 1%_06( R )

CPU_D#3

CPU_A#19

C 81 .1U _X7R _04

CPU_D#58

VC ORE

CPU_DBI0#

CPU_A#27

CPU_A#21

CPU_A#32

C108

.1U_X7R_04

CPU_ADSTB0#

CPU_D#45

CPU_DSTBN0# 5

VC ORE

CPU_A#15

CPU_A#10

CPU_D#42

C482

10U /10V _08

CPU_REQ#4

CPU_GTLREF3

C 114 .1 U_ X7R_0 4

CPU_D#4

CPU_A#5

CPU_D#47

CPU_D#11

CPU_GTLREF2_DIVIDER

CPU_D#46

CPU_DSTBN2# 5

CPU_D#29

CPU_ADSTB1#

R88

210_ 1%_06

CPU_DBI3#5

C493

10U /10V _08

CPU_LOCK#5

+

C71

470U F/ 2.5V _D2( R )

12

CPU_D#21

TESTHI_10

CPU_GTLREF2

CPU_HIT#5

CPU_D#18

R 79 62_1%_06

CPU_D#60

U19D

CPU LGA775-P4_21

AM29

AM30

AM8

AM9

AN11

AN12

AN14

AN15

AN18

AN19

AN21

AN22

AN25

AN26

AN29

AN30

AN 8

AN 9

J10

J11

J12

J13

J14

J15

J18

J19

J20

J21

J22

N25

N26

N27

N28

N29

N30

N8

P8

R8

T23

T24

T25

T26

T27

T28

T29

T30

T8

U23

U24

J23

J24

J25

J26

J27

J28

J29

J30

J8

J9

K23

K24

K25

K26

K27

K28

K29

K30

K8

L8

M23

M24

M25

M26

U25

U26

U27

U28

U29

U30

U8

V8

W23

W24

W25

W26

W27

W28

W29

W30

W8

Y23

Y24

Y25

Y26

Y27

Y28

Y29

Y30

Y8

M29

M30

M8

N23

N24

M27

M28

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC ORE

CPU_A#9

CPU_D#59

CPU_RS#1

C496

10U /10V _08

CPU_A#11

CPU_BNR#

HOST DATAHOST DATA

HOST ADDRESS

U19A

CPU LGA775-P4_21

L5

P6

M5

L4

M4

R4

T5

U6

T4

U5

U4

V5

V4

W5

N4

P5

K4

J5

M6

K6

J6

R6

G5

AB6

W6

Y6

Y4

AA4

AD 6

AA5

AB5

AC 5

AB4

AF5

AF4

AG6

AG4

AG5

AH 4

AH 5

AJ5

AJ6

AD 5

D2

C2

D4

H4

G8

B2

C1

E4

AB2

P3

C3

E3

AD 3

G7

F2

AB3

U2

U3

F3

G3

G4

H5

J16

H15

H16

J17

H1

G23

B3

F5

A3

B4

C5

A4

C6

A5

B6

B7

A7

A10

A11

B10

C11

D8

B12

C12

D11

A8

C8

B9

G16

E15

E16

G18

G17

F17

F18

E18

E19

F20

E21

F21

G21

E22

D22

G22

D19

G20

G19

G9

F8

F9

E9

D7

E10

D10

F11

F12

D13

E13

G13

F14

G14

F15

G15

G11

G12

E12

D20

D17

A14

C15

C14

B15

C18

B16

A17

B18

C21

B21

B19

A19

A22

B22

C20

A16

C17

G1

A03#

A04#

A05#

A06#

A07#

A08#

A09#

A10#

A11#

A12#

A13#

A14#

A15#

A16#

RSVD

RSVD

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

AD STB0 #

PC _REQ #

A17#

A18#

A19#

A20#

A21#

A22#

A23#

A24#

A25#

A26#

A27#

A28#

A29#

A30#

A31#

A32#

A33#

A34#

A35#

AD STB1 #

AD S#

BN R#

HIT#

RSP#

BPR I#

DBSY#

DRDY#

HITM#

IERR#

INIT#

LOC K#

TRDY#

BIN IT #

DEFER#

ED RD Y#

MCERR#

AP0#

AP1#

BR 0#

TESTHI08

TESTHI09

TESTHI10

DP0#

DP1#

DP2#

DP3#

GT LREF

RESET#

RS0#

RS1#

RS2#

D00#

D01#

D02#

D03#

D04#

D05#

D06#

D07#

D08#

D09#

D10#

D11#

D12#

D13#

D14#

D15#

DBI0#

DSTBN0#

DSTBP0#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

DBI2#

DSTBN2#

DSTBP2#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

DBI1#

DSTBN1#

DSTBP1#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DBI3#

DSTBN3#

DSTBP3#

RSVD

CPU_D#61

TP_CPU_G1

CPU_D#32

VTT_OUT_RIGHT

C91

.1U_X7R_04

VTT_OUT_RIGHT

C PU _AD ST B1#5

VTT_OL 4

CPU_D#34

1.2VS

C PU_ ADS#5

CPU_A#25

CPU_REQ#2

C106

.1U_X7R_04

CPU_D#[0..15]5

CPU_D#[32..47] 5

CPU_D#50

CPU_D#7

CPU_D#10

CPU_INIT#

1. 2VS 4. .6, 9, 12,15 ..1 7,30

CPU_D#17

CPU_DBI3#

VC ORE

VCORE

CPU_A#13

CPU_A#18

R81 51_04

C132

1U_04

VCORE 34

TESTHI_9

CPU_GTLREF3_DIVIDER

CPU_DBI0#5

CPU_D#30

CPU_HITM#5

CPU_DSTBN1# 5

CPU_A#12

CPU_D#56

R 68 62_1%_06

CPU_A#14

CPU_DBSY#

CPU_A#31

C494

10U /10V _08

CPU_DSTBP3# 5

CPU_D#55

CPU_A#23

CPU_RS#0

C115

220P_04(R)

C498

.1U_X7R _04

CPU_D#37

C104

10U /10V _08

C490

10U /10V _08

C 528

1U_04(R)

CPU_GTLREF3 4

CPU_DSTBN2#

CPU_D#40

U19C

CPU LGA775-P4_21

AA8

AB8

AC23

AC24

AC25

AC26

AC27

AC28

AC29

AC30

AC 8

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD 8

AE11

AE12

AE14

AE15

AE18

AE19

AE21

AE22

AE23

AE9

AF11

AF12

AF14

AF15

AF18

AF19

AF21

AF22

AF 8

AF 9

AG11

AG12

AG14

AG15

AG18

AG19

AG21

AG22

AG25

AG26

AG27

AG28

AG29

AG30

AG8

AG9

AH11

AH12

AH14

AH15

AH 18

AH 19

AH 21

AH 22

AH 25

AH 26

AH 27

AH 28

AH 29

AH 30

AH 8

AH 9

AJ1 1

AJ1 2

AJ1 4

AJ1 5

AJ1 8

AJ1 9

AJ2 1

AJ2 2

AJ2 5

AJ2 6

AJ8

AJ9

AK11

AK12

AK14

AK15

AK18

AK19

AK21

AK22

AK25

AK26

AK8

AK9

AL11

AL12

AL14

AL15

AL18

AL19

AL21

AL22

AL25

AL26

AL29

AL30

AL8

AL9

AM 11

AM 12

AM 14

AM 15

AM 18

AM 19

AM 21

AM 22

AM 25

AM 26

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

VC C

PECI10

CPU_DSTBN0#

C497

.1U_X7R_04

C483

10U /10V _08

CPU_BR0#5

CPU_DBI2#5

CPU_GTLREF0 4

CPU_D#35

CPU_D#48

CPU_A#30

CPU_REQ#1

C484

10U /10V _08

CPU_GTLREF3

R83

124_ 1%_04

C78

10U /10V _08

CPU_D#2

C94

1U_04(R)

VC ORE

CPU_A#29

CPU_DSTBP1# 5

CPU_RS#[0..2]5

CPU_D#6

VTT_OUT_RIGHT

C PU_ ADST B0#5

CPU_DRDY#5

CPU_D#12

TESTHI_8

C95 .1U_X7R_04

CPU_D#20

R 50 10_04 (R )

CPU_HITM#

CPU_A#3

CPU_A#22

+

C47

470U F/ 2.5V _D2( R )

12

C PU_ A#[17. .35 ]5

CPU_BPRI#

R497 51_04

VC ORE

CPU_D#22

R48

124_ 1%_04( R )

VTT_OUT_LEFT

CPU_ADS#

CPU_REQ#[0..4]

C93

10U /10V _08

CPU_BNR#5

CPU_D#[48..63] 5

VTT_OR 4,34

C489

10U /10V _08

CPU_A#26

CPU_DSTBP3#

CPU_D#43

C88

.1U_X7R_04

C110

220P_04(R)

VTT_OUT_RIGHT

CPU_DBI1#5

CPU_HIT#

CPU_DSTBN3#

R54 0_04(R)

VT T_OU T _RI GHT

CPU_TRDY#

CPU_LOCK#

VTT_OUT_LEFT

R80 51_04

VTT_OUT_LEFT

CPU_GTLREF2

CPU_D#62

CPU_DSTBP0#

CPU_A#34

+

C 124

470U F/ 2.5V _D2( R )

12

CPU_D#0

CPU_D#49

CPU_D#36

C59 .1U_X7R_04

CPU_A#4

CPU_GTLREF0

CPU_GTLREF0_DIVIDER

CPU_D#28

C80

10U/10V_08

C56

.1U_X7R _04

C486

10U /10V _08

C99

.1U_X7R_04

CPU_D#51

CPU_D#33

C 79 .1U _X7R _04

CPU_IERR#

CPU_A#20

CPU_REQ#0

VC ORE

VC ORE

CPU_DSTBP2#

CPU_A#6

CPU_D#9

CPU_REQ#[0..4]5

CPU_DBI2#

CPU_D#54

C131

220P_04

VTT_OUT_LEFT

CPU_DEFER#

C495

10U /10V _08

C107 .1U_X7R_04

R507

124_ 1%_04( R )

CPU_D#1

CPU_BR0#

R76 51_04

C487

10U /10V _08

C481

10U /10V _08

CPU_A#24

CPU_RS#2

CPU_D#52

R75 10_04(R)

CPU_DSTBP1#

CPU_D#24

CPU_D#13

C103

10U /10V _08

CPU_D#[16..31] 5

CPU_DSTBP2# 5

CPU_RST#

R 34 62_1 %_06

CPU_TRDY#5

CPU_A#28

CPU_D#63

CPU_A#35

R 84 10_0 4

VCORE

CPU_DSTBN3# 5

CPU_GTLREF2

CPU_A#16

CPU_D#38

CPU_D#8

CPU_DBI1#

CPU_RS#[0..2]

CPU_GTLREF0

VC ORE

CPU_A#[3..16]5

CPU_D#26

CPU_DSTBN1#

CPU_D#41

C 105

.1U_X7R_04

CPU_REQ#3

CPU_D#16

CPU_D#5

CPU_D#39

C75

10U /10V _08

R511

210_ 1%_06( R )

CPU_RST#5

CPU_D#57

CPU_D#44

CPU_DBSY#5

+

C98

470U F/ 2.5V _D2( R )

12

CPU_INIT#10

CPU_D#19

CPU_A#7

CPU_A#17

CPU_DRDY#

CPU_D#14

Sheet 3 of 40

CPU-1