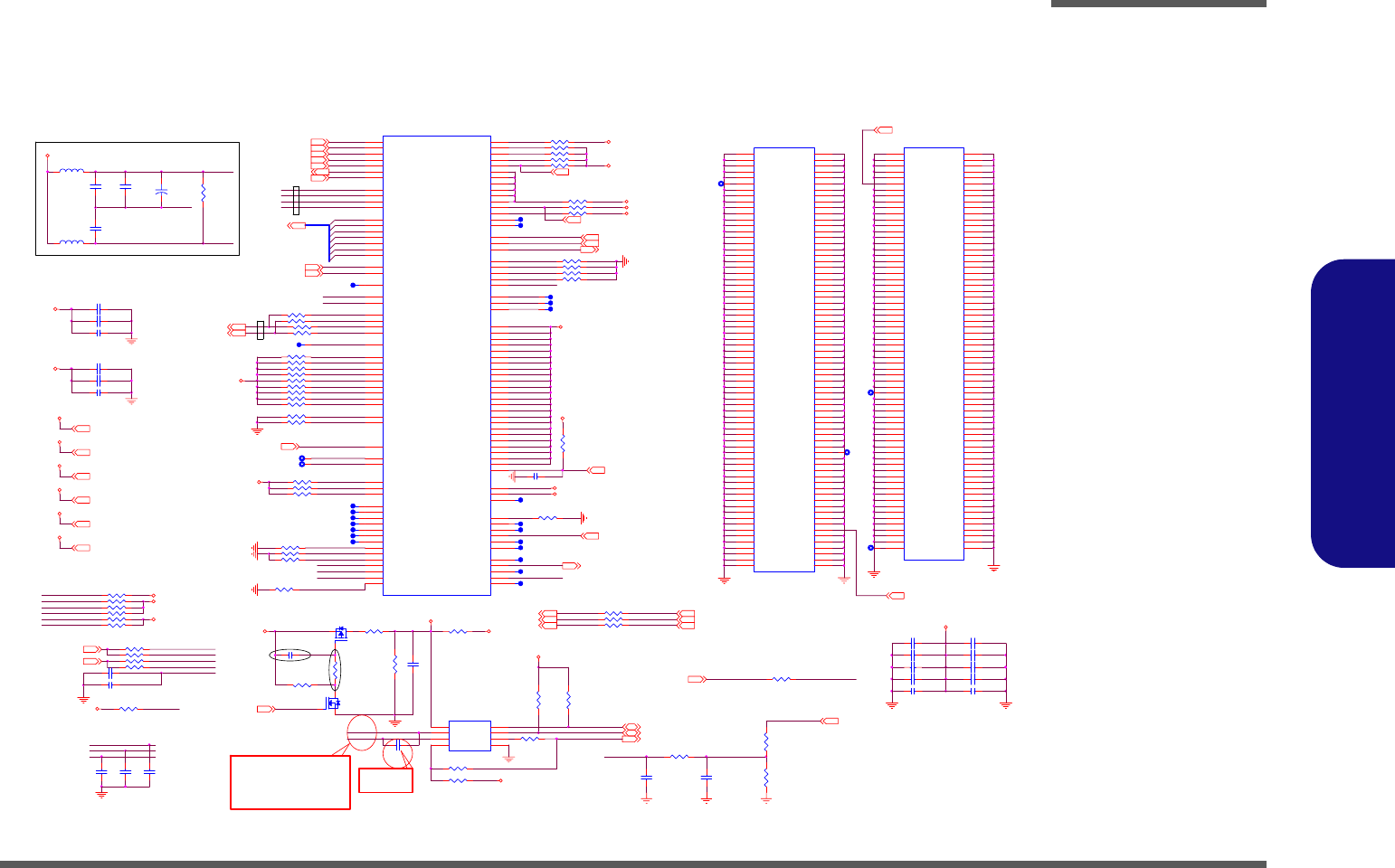

Schematic Diagrams

CPU-2 B - 5

B.Schematic Diagrams

CPU-2

Sheet 4 of 40

CPU-2

CPU_STPCLK#10

R500 49.9_1%_04

R4 99 150_1% _04

R474

4.7K_04

H_TDO

CPU_COMP7

THERMDC

TESTHI_2-7

Near to

F75383M

VTT_PKGSENSE

C57 10U/10V_08

C125 .1U_X7R_04

C988

.1U_X7R_04(R)

1. 5VS 9. .13 ,25, 28,3 3

VCC_SENSE

FSBSEL22

R493 47_04

R85 0_04( R)

1.5V S

C6 7 10U /10V _08

MC H_ BSEL1

U19B

CPU LGA775-P4_21

P2

K3

R3

K1

L1

N2

M3

A23

B23

D23

C23

AE8

AM2

AL5

AM3

AL6

AK4

AL4

AM5

F28

G28

AL1

AK1

AN3

AN4

AN5

AN6

F29

AE1

AD1

AF1

AC1

AG1

AJ2

AJ1

AD2

AG2

AF2

AG3

AC2

AK3

AJ3

G29

H30

G30

F26

W3

P1

W2

F25

G25

G27

G26

AK6

G6

L2

AH2

N1

AL2

M2

A13

T1

G2

R1

Y1

V2

AA2

A25

A26

A27

A28

A29

A30

B25

B26

B27

B28

B29

B30

C25

C26

C27

C28

C29

C30

D25

D26

D27

D28

D29

D30

AM6

AA1

J1

F27

G24

F24

N5

AE6

C9

G10

D16

A20

E23

E24

F23

H2

J3

AC4

AE3

AE4

D1

D14

E5

E6

E7

F6

B13

T2

V1

W1

Y3

U1

J2

SM I#

A20M #

FE RR #/PBE#

LIN T0

LIN T1

IGNNE#

ST PCLK#

VC CA

VSSA

VC C_PLL

VC CIO PLL

SKT OCC #

VID 0

VID 1

VID 2

VID 3

VID 4

VID 5

VID 6

BC LK0

BC LK1

THERMDA

THERMDC

VC C_SEN SE

VSS_S ENSE

RSVD

RSVD

VT T_PKG SENSE /RS VD

TCK

TDI

TDO

TMS

TRST#

BPM 0#

BPM 1#

BPM 2#

BPM 3#

BPM 4#

BPM 5#

DBR#

ITP_CLK0

ITP_CLK1

BSEL0

BSEL1

BSEL2

TESTHI00

TESTHI01

TESTHI11

TESTHI12

TESTHI02

TESTHI03

TESTHI04

TESTHI05

RSVD

RSVD

TESTHI13

RSVD

PWRG OOD

PR OCH OT#

THERMTRIP#

COMP0

COMP1

COMP2

COMP3

BOOTSELECT

LL_ID0

LL_ID1

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VT TPWRG D

VTT _OUT

VTT _OUT

VT T_SEL

TESTHI06

TESTHI07

SPAR E0

SPAR E4

SPAR E1

RSVD

NC_DSS2

NC_DSS3

NC

NC

EXT BGR EF

NC

ACLK PH

RSVD

COMP7

RSVD

HFPLL

SF RAN AD

DCLKPH

SF RAN AC

SPAR E2

RSVD

COMP8

COMP5

RSVD

RSVD

COMP6

RSVD

COMP4

T ESTH I_11

D05

CPU_COMP3

CPU_STPCLK#

VD D3

CPU_BPM#1

CPU_NMI

CPU_NMI

T

R4 87 49 .9_1 %_04

L4

LB2012T 100M

THERM_RST#

T

T

H_FORCEPH_N 34

CPU_THERMTRIP#

CPU_THERMTRIP#

CPU_COMP1

1.2VS

VTT_OUT_R IGHT

THM_VDD

H_ITPCLK

CPU_MSID1

R 62 4 9.9_ 1%_04

CPU_ GTLREF0

R495 49.9_1%_04

+

C83

22U _08

12

VTT_OU T_R I GHT

CPU_IGNNE#10

R4 91 62 _1%_06

R488 51_04

C510

2200P_04

1.2 VS

CPU_VID4

R 485 62_1% _06

C 982

.1U_04(R)

R6 6 10 0_04( R )

CPUCLK#

CPU_COMP7

VC CIO PLL

C77

1U_04

THM_VDD

R501 47_04

R67 0_04

FSBSEL12

CPU_BPM#4

T ESTH I_12

R69 47_04

VTT_OL3

TESTHI_13 10

CPU_IGNNE#

TH ER MDC

VCC_MB_REG

R63

1K_04

CPUCLK2

U20

G781- 1

8

7

6

54

3

2

1

SCLK

SDATA

ALER T#

GN DTHERM#

D-

D+

VDD

CPU_FERR#

MC H_ BSEL2

Q38

AO340 9(R )

G

DS

R732

0_04

C32 10U/10V_08

H_TCK

SMD_THERM

R78 51_1%_04

CPUPWRGD

R 41 0 _06

R86

10_04

CPUPWRGD 11

CPU_GTLREF3 3

CPU_NMI

CPU_COMP8

R42

0_04

C126 10U/10V_08

C58 .1U_X7R_04

CPU_BPM#5

FSBSEL2

R72 47_04

C509

1000P _04

1.2V S

VTT_OU T_R IGH T

CPU_FERR#10

H_PROCHOT_N

CPU_SMI#

C129 .1U_X7R_04

R77 0_04( R)

VTT_O U T_LE FT

CPU_V ID7 34

M CH _BSEL0 6

C82

10U /10V_08

R 71 4 9.9_ 1%_04

10 MILE

VTT_ OU T_R IG HT

CPU_GTLREF1

CPU_MSID0

R1 1 470 _06

R74 0_04( R)

H_CPU_PD_F6

TH ER MDA

C130

220P_04

R 486 51_04

VTT_OUT_RIGHT 3,34

CPU_VID6

1.2 VS

CPU_CORE_FB+34

CPU_VID3

R57 51_04

10mil

C506

1U_06

R4 94 49 .9_1 %_04

R504

210_1%_06

VTT_OUT_LEFT3

R471 0_04

R 479 62_04

CPU_MCH_GTLREF 5

T ESTH I_13

R56 124_1% _04( R)

THERM_RST#23

VTT_OUT_RIGHT

R475

4.7K_04

CPU_VID[0..6]34

M CH _BSEL1 6

R32 is Reserved for ADT1032ARM

VRM_PWRGD 11,34

VCCIOPLL

VSS_SENSE

R 43 24.9_ 1%_04

FSBSEL1

CPU_ V IDSEL 34

12 MIL TRACE

VTT_OUT_LEFT

C34 10U/10V_08

R466

0_04(R)

20 mil

CPU_CORE_FB-34

CPU_BPM#0

CPU_COMP6

CPU_THERMTRIP# 10

T

SYS_ RST #11

M CH _BSEL2 6

CPU_COMP0

FSBSEL0

MC H_ BSEL0

CPUCLK

TESTHI_0

CPU_FERR#

VTT_OUT_RIGHT

CPU_NMI10

VD D3 1 3,1 9,23, 25. .27, 29,3 2,33

FSBSEL1

R465

100K_0 4( R)

1.2 VS

3V

Do'nt cross to high speed signal

CPU_INTR10

CPU_GTLREF1

R5 02 150_1% _04

CPU_COMP2

CPU_INTR

C31 .1U_X7R_04

CPU_BPM#2

R15 10K_04

1. 5VS

CPU_VID2

T

R4 64 124_04 (R )

R60 1K_04

R9 10K_04

SMC_THERM 14,23

C511

1000P _04

VD D3

VTT_OR 3,34

H _FOR CEPH _N

C48 10U/10V_08

DIFF PAIR

Layout Note:

Route H_THERMDA and

H_THERMDC on same layer.

10 mil trace on 10 mil

spacing.

CPU_A20M#10

U19F

CPU LGA775-P4_21

AN 20

AN 23

AN 24

AN 27

AN 28

AN7

B1

B11

B14

B17

B20

B24

B5

B8

C10

C13

C16

C19

C22

C24

C4

C7

D12

D15

D18

D21

D24

D3

D5

D6

D9

E11

E14

E17

E2

E20

E25

E26

E27

E28

E29

E8

F10

F13

F16

F19

F22

F4

F7

H10

H11

H12

H13

H14

H17

H18

H19

H20

H21

H22

H23

H24

H25

H26

H27

H28

H29

H7

H8

H9

J4

J7

K2

K5

K7

L23

L24

L25

L26

L27

L28

L29

L30

L3

L6

L7

M1

M7

N3

N6

N7

P23

P24

P25

P26

P27

P28

P29

P30

P4

P7

R2

R23

R24

R25

R26

R27

R28

R29

R30

R5

R7

T3

T6

T7

U7

V23

V24

V25

V26

V27

V28

V29

V30

V3

V6

V7

W4

W7

Y2

Y5

Y7

H3

H6

VSS

VSS

VSS

VSS

VSS

VID SELEC T

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

GTL REF _SEL

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

C120

.01U_04

VTT_OU T_LE FT

SYS_RST#

THERMDA

CPU_COMP4

CPU_COMP5

VCCPLL

C524

1U_04

R4 67 100 K_04( R )

VTT_OU T_LE FT

SMD_THERM 14,23

FSBSEL0

R8 470_06

R476 0_04(R)

C61

1U_04

R 483 51_1% _04

As close as possible to CPU socket

1. 2VS 5, 6,9 ,12, 15.. 17,3 0

CPU_COMP5

FSBSEL2

VC CA

R82 51_1%_04

T

CPU_BPM#3

VCCPLL

R 482 62_1% _06

CPU_VID5

CPU_INTR

CPU_VSSA

THERM_ALERT# 23

3V6,10..13,21,25..28,30..33

THERM_ALERT#

VTT_OUT_LEFT

CPU_GTLREF1

1.2VS

H_TDI

R496

124_1%_04

R 478 51_1% _04

R470 10K_04

CPU_VID1

L5

LB2012T 100M

10 MILE

C133 10U/10V_08

3V

VC CPLL

C53

.01U_04

CPU_SMI#10

CPU_GTLREF03

VR M_PWR GD

R70 0_04

R1 4 470 _06

R 477 51_1% _04

R22 51_04

H_TRST_N

1.2VS

TP_V2

CPU_COMP6

R4 98 49 .9_1 %_04

R12 10K_04

C60

.01U_04

CPUCLK#2

VT T_OU T_R IGH T3,34

BOOTSEL

C36 .1U_X7R_04

R21 47_04

C55 .1U_X7R_04

R4 4 49. 9_1%_04

CPU_COMP4

TH ER MDC

VCCA_VSSA_VCOREPLL Trace width donesn't less than 12 Mil

CPU_GTLREF3

CPU_GTLREF1_DIVIDER

R 480 51_1% _04

R4 89 51_04

CPU_VSSA

R5 5 62 _1%_06

H_ITPCLK#

H_PROCHOT_N 10,34

TESTHI_1

H_PROCHOT_N

TP_AA2

VCCPLL

Q39

2N 7002W( R)

G

DS

R4 90 51_04

C127

.01U_04

D05

1.2VS

C54

.01U_04

VTT_O U T_R IG HT

3V

TH ER MDA

R73 51_1%_04

U19E

CPU LGA775- P4_21

A12

A15

A18

A2

A21

A24

A6

A9

AA23

AA24

AA25

AA26

AA27

AA28

AA29

AA3

AA30

AA6

AA7

AB1

AB23

AB24

AB25

AB26

AB27

AB28

AB29

AB30

AB7

AC3

AC6

AC7

AD4

AD7

AE10

AE13

AE16

AE17

AE2

AE20

AE24

AE25

AE26

AE27

AE28

AE29

AE30

AE5

AE7

AF10

AF13

AF16

AF17

AF20

AF23

AF24

AF25

AF26

AF27

AF28

AF29

AF30

AF3

AF6

AF7

AG10

AG13

AG16

AG17

AG20

AG23

AG24

AG7

AH 1

AH 10

AH 13

AH 16

AH 17

AH 20

AH 23

AH 24

AH 3

AH 6

AH 7

AJ1 0

AJ1 3

AJ1 6

AJ1 7

AJ2 0

AJ2 3

AJ2 4

AJ2 7

AJ2 8

AJ2 9

AJ3 0

AJ4

AJ7

AK10

AK13

AK16

AK17

AK2

AK20

AK23

AK24

AK27

AK28

AK29

AK30

AK5

AK7

AL10

AL13

AL16

AL17

AL20

AL23

AL24

AL27

AL28

AL3

AL7

AM 1

AM 10

AM 13

AM 16

AM 17

AM 20

AM 23

AM 24

AM 27

AM 28

AM 4

AM 7

AN 1

AN 10

AN 13

AN 16

AN 17

AN 2

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VI D7/ VSS

VSS

VSS

VSS

VSS

VSS

VSS

CPU_VID0

CPU_A20M#

VT T_OU T_R IGH T

VSS_MB_REG

R 860

10_04( R )

to H8 & S.B.

VTT_OUT_LEFT

H_TMS

C128

.01U_04

FSBSEL02

VCCA