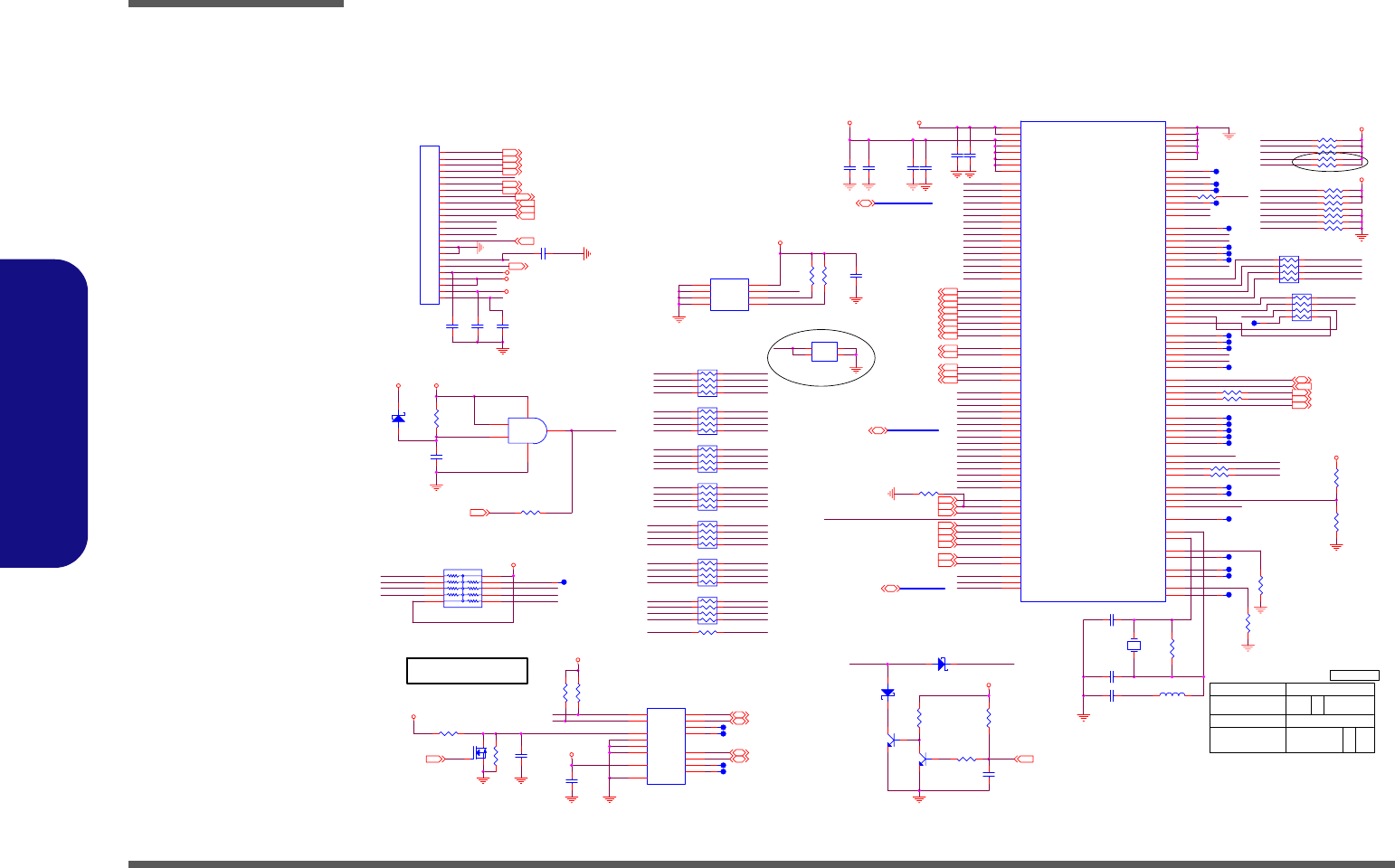

Schematic Diagrams

B - 22 AUDIO-DJ

B.Schematic Diagrams

AUDIO-DJ

Sheet 21 of 40

AUDIO-DJ

CDD5

PDIORDY

LED_PWRON

R367 10

+3VCDROM

PIDED3

PIDED13

C_ACRST#

CDA2

+3VCDROM

CDIOWN12

C_BITCLK

C_SYNC

I2C Address C D E F

VOLUM_UP

SD_DAT1 0 0 1 1

+3VCDROM

RD

SRS_SW#

PIDED11

KEY4

R358 10K

+3VCDROM CDD9

PIDED10

PIDED10

CINTRQ

PDIOW#

PDDACK#

SATALED# 12

CDD10

F_DD7 0 0 1 1 0

STOP_EJECT

CDA1

CINTRQ

CDD3

KEY7

REP_LED

VOLUM_UP 25

SD_DAT1

ADJ_SMDATA

Q12

2N7002

G

DS

CIORDY

C_SDIN2

PIDED6

PIDED4

R606

1K

C405

0.1UF

R378

30K

PDDACK#

PIDED12

CDD14

C515

0.1UF

CDMACKN12

ADJ_SMCLK

PIDED1

PDLEDA#

CDD10

C129 1000PF

PDA[0..2]12

SD_DAT2

R356 10K

R372 *5.6K

VOLUM_DOWN 25

PCIRST#11,15,17,24,25

LED_PWRON

H8ADJ_RESET#25

BB_WP

FF

CCS1

BlueBirdVL

/ VL+

U12

BlueBird VL+

101

25

32

56

94

113

80

120

47

73

108

87

9

16

1

3

7

10

14

17

19

12

5

2

4

8

11

15

18

20

22

6

13

88

89

90

92

93

91

48

49

50

51

52

53

54

55

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

76

75

77

74

78

79

81

82

83

84

85

86

26

28

30

33

35

27

29

31

34

36

37

46

38

45

39

40

41

42

43

44

21

96

98

100

95

97

99

103

102

105

104

107

110

112

115

119

124

126

106

109

111

114

118

123

125

23

24

116

117

122

121

128

127

VCC5

VCC5

VDD

VDD

VDD

VDD

VDD

VSS

VSS

VSS

VSS

VSS

VDD

VSS

C_DD8

C_DD9

C_DD10

C_DD11

C_DD12

C_DD13

C_DD14

C_DMARQ

C_DIOW#

H_DD8

H_DD9

H_DD10

H_DD11

H_DD12

H_DD13

H_DD14

H_DD15

H_DIOW#

H_DMARQ

C_DASP#

H_DASP#

C_CS1

C_CS0

H_CS0

H_CS1

port1[0]/F_DD0

port1[1]/F_DD1

port1[2]/F_DD2

port1[3]/F_DD3

port1[4]/F_DD4

port1[5]/F_DD5

port3[4]/F_DD6

port3[5]/F_DD7

port3[1]/F_RE

port3[3]/F_WE

port3[0]/F_CE

SD_LED/F_CLE

SD_MCD/F_ALE

SD_MWP/F_SE

port3[2]/F_RB

KEY0

KEY1

KEY2

KEY3

KEY4

KEY5

KEY6

KEY7

port3[6]/OSC32

XTALI48

XTALI245

XTALO48

XTALO245

USB-

USB+

SD_CLK

SD_CMD/I2CID[4]

SD_DAT0/I2CID[0]

SD_DAT1/I2CID[1]

SD_DAT2/I2CID[2]

SD_DAT3/I2CID[3]

C_BCLK

C_SDIN

C_CDOUT

C_SYNC

C_ACRST#

H_BCLK

H_SDIN

H_SDOUT

H_SYNC

H_ACRST#

TESTO

TEST

INTR#

RST#

IIC1C

IIC1D

IIC2C

IIC2D

PWR_DN

MODE_SELECT

C_DD15

H_DA2

H_DA0

H_DA1

C_DA2

C_DA0

C_DA1

H_INTRQ

C_INTRQ

H_DD0

C_DD0

H_DD1

H_DD2

H_DD3

H_DD4

H_DD5

H_DD6

H_DD7

C_DD1

C_DD2

C_DD3

C_DD4

C_DD5

C_DD6

C_DD7

C_RESET

H_RESET

C_DMACK#

H_DMACK#

H_DIORDY#

C_DIORDY#

H_DIOR#

C_DIOR#

PIDED2

PDCS#3

PIDED3

CCS1

VOLUM_DOWN

CDA212

H8LED_CLK1

RP15 *8P4RX0_0402

8 1

7 2

6

5

3

4

R365 10

H8LED_DATA 25

PLAY_PAUSE

PIDED9

PIDED8

C111

*0.1UF

RP5

8P4RX47_0402

8 1

7 2

6

5

3

4

PIN14(S0):LOW-->H8

H8_RESET#

CDD15

R596 0

R94

1.5K

KEY5

CRESETN

C110

0.1UF

CDA012

CDD6

CDD14

PDIOW#12

PCIRST#

FF

CCS0

BBLED_DATA

C517

0.1UF

CDMACKN

C404

*0.1UF

REP_SW# 25

CRESETN12

C_SDOUT

BBLED_CLK

PIDED5

STOP_EJECT

CDD4

IRQ14

D45

1SS355

A C

F_WE 0 0 0 0 1

H8LED_CLK1 25

R364

1K

J-ADJ1

CON24

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

CDMARQ12

BUS_SEL

CDD1

PDLED#

CDMACKN

C516

0.1UF

HIGH : BYPASS

LOW : AUDIO-DJ

CDIOWN

CDD9

R602 *0

SD_DAT2 0 1 0 1

R369 10K

C733

*0.1UF

RP16 *8P4RX0_0402

8 1

7 2

6

5

3

4

+5VCDROM

CDD[0..15]12

RD

KEY6

PDDREQ

H8LED_CLK2 25

PDDREQ12

STOP_EJECT

VOLUM_UP

PIDED15

PIDED6

Q37

2N3904

B

E C

+3VS

F_WE

MODE_SELECT

BB_WP

RP13 *8P4RX0_0402

8 1

7 2

6

5

3

4

R264

3.3K

CDIOWN

PDA1

I2C Header 0 1 2 3 4

+VDD5

R265

2.7K

R362

680

+5VCDROM

CDPWRBTN# 30

PDIORDY12

CDD[0..15]

C_BITCLK 20

CDD3

IRQ1412

CDD6

R374 47

U6 24LC256P

1

2

3

4 5

6

7

8

A0

A1

NC/A2

VSS SDA

SCL

WP

VCC

STOP_EJECT 25

CDA1

BBLED_STB

PDCS#3

+3VS

C_ACRST#

CDD4

R118

5.1M

C519

0.1UF

PDA[0..2]

PIDED0

PIDED9

PDIOW#

CIORDY

KEY1

VOLUM_UP

CRESETN

PIDED7

R366 4.7K

CDA112

PCIRST#

F_WE

IRQ14

Default Setting

PLAY_PAUSE 25

ADJ_RESET#

CDD11

R363 10K

C108 0.1UF

SMBDATA 2,8,9,11,18,19

C_ACRST# 20

CDA0

SD_DAT1

CDD12

PIDED7

PDLED#

VOLUM_DOWN

CDD13

C_SDOUT 20

F_DD7

PIDED11

PDLED#

R605

1K

+3VCDROM

REP_LED

C128 18PF

RP19 *8P4RX0_0402

8 1

7 2

6

5

3

4

CDIORN12

CDD0

PIDED8

R267

10K

+5VS

PDIOR#12

H8LED_CLK2

PLAY_PAUSE

RD

ADJ_SMDATA

CDD2

ADJ_SMCLK

C127 18PF

C518

0.1UF

D7

RB751V

A C

設定在

A0

的位置

CDIORN

+3VCDROM

C_SDOUT

C_SDIN2

PDA0

R357 10K

CDD7

PIDED2

F_DD7

R373 10K

H8_SMCLK-B 10,25,30

PIDED0

RP18 *8P4RX0_0402

8 1

7 2

6

5

3

4

CIORDY

F_DD6

KEY2

SD_DAT2

CDD7

R360 10K

VOLUM_DOWN

D46

1SS355

AC

PDCS#312

L23

2.7UH

100ms

PIDED[0..15]

RP3

10P8RX10K

10

9

8

7

6

1

2

3

4

5

RP4 8P4RX47_0402

8 1

7 2

6

5

3

4

JP1

CON4

12

34

REP_SW#

PDDREQ

R375 10K

R595 *0

REP_SW#

CDD1

CDD11

BB_WP

+5VCDROM

CCS112

CIORDY12

CDMARQ

PDIORDY

PIDED14

R355 10K

CDASPN

H8_SMDATA-B 10,25,30

CDD15

CDMARQ

PDLEDA#

R607

8.2K

+3VS

F_DD6

PDIOR#

CDMACKN

PIDED1

CDD12

CDA0

Q38

2N3904

B

E C

R601 10K

+5VCDROM

SMBCLK 2,8,9,11,18,19

CCS012

CDD2

KEY3

PIDED5

+3VCDROM

CDPWRBTN#

CDD8

ADJ_RESET#

U11

*7S08

1

2

4

53

R371 *10K

F_DD6 0 1 0 1 0

C_SYNC 20

CDASPN12

FF

VL+ AB I2C CONFIGURATIONS

FF 25

PIDED13

BBLED_DATA

CDD8

C513

0.1UF

PDA2

PDCS#1

PDA0

C126

10UF/6.3V

PIDED4

C514

0.1UF

R266 1K

BBLED_STB

CDA2

ICH6_ADJ#11

C_SDIN2 20

PDDACK#12

CCS0

KEY0

PIDED15

R359

2.7K

R93

1.5K

PLAY_PAUSE

PIDED14

PIDED[0..15]12

RD 25

CDMARQ

H8LED_DATA

R370 47

CINTRQ12

PDCS#112

BBLED_CLK

CDD0

PDA1

CDD5

Y2

48MHz

12

PDCS#1

RP17 *8P4RX0_0402

8 1

7 2

6

5

3

4

BBLED_DATA

BBLED_CLK

CDD13

PDA2

CDIORN

R368

2.7K

HIGH-->ICH6

PDIOR#

PIDED12

H8_RESET# 25

CDASPN

BB_WP

C109

0.1UF

RP14 *8P4RX0_0402

8 1

7 2

6

5

3

4

U30

QS3253

6

5

4

3

10

11

12

13

7

9

14

2

1

15

16

8

1A

2A

3A

4A

1B

2B

3B

4B

YA

YB

S0

S1

AOE#

BOE#

VCC

GND