CY2291

Three-PLL General Purpose EPROM

Programmable Clock Generator

Cypress Semiconductor Corporation • 198 Champion Court • San Jose, CA 95134-1709 • 408-943-2600

Document #: 38-07189 Rev. *C Revised September 16, 2008

Features

■ Three integrated phase-locked loops

■ EPROM programmability

■ Factory-programmable (CY2291) or field-programmable

(CY2291F) device options

■ Low-skew, low-jitter, high-accuracy outputs

■ Power-management options (Shutdown, OE, Suspend)

■ Frequency select option

■ Smooth slewing on CPUCLK

■ Configurable 3.3V or 5V operation

■ 20-pin SOIC Package

Benefits

■ Generates up to three custom frequencies from external

sources

■ Easy customization and fast turnaround

■ Programming support available for all opportunities

■ Meets critical industry standard timing requirements

■ Supports low-power applications

■ Eight user-selectable frequencies on CPU PLL

■ Allows downstream PLLs to stay locked on CPUCLK output

■ Enables application compatibility

■ Industry-standard packaging saves on board space

Part Number Outputs Input Frequency Range Output Frequency Range Specifics

CY2291 8 10 MHz–25 MHz (external crystal)

1 MHz–30 MHz (reference clock)

76.923 kHz–100 MHz (5V)

76.923 kHz–80 MHz (3.3V)

Factory Programmable

Commercial Temperature

CY2291I 8 10 MHz–25 MHz (external crystal)

1 MHz–30 MHz (reference clock)

76.923 kHz–90 MHz (5V)

76.923 kHz–66.6 MHz (3.3V)

Factory Programmable

Industrial Temperature

CY2291F 8 10 MHz–25 MHz (external crystal)

1 MHz–30 MHz (reference clock)

76.923 kHz–90 MHz (5V)

76.923 kHz–66.6 MHz (3.3V)

Field Programmable

Commercial Temperature

CY2291FI 8 10 MHz–25 MHz (external crystal)

1 MHz–30 MHz (reference clock)

76.923 kHz–80 MHz (5V)

76.923 kHz–60.0 MHz (3.3V)

Field Programmable

Industrial Temperature

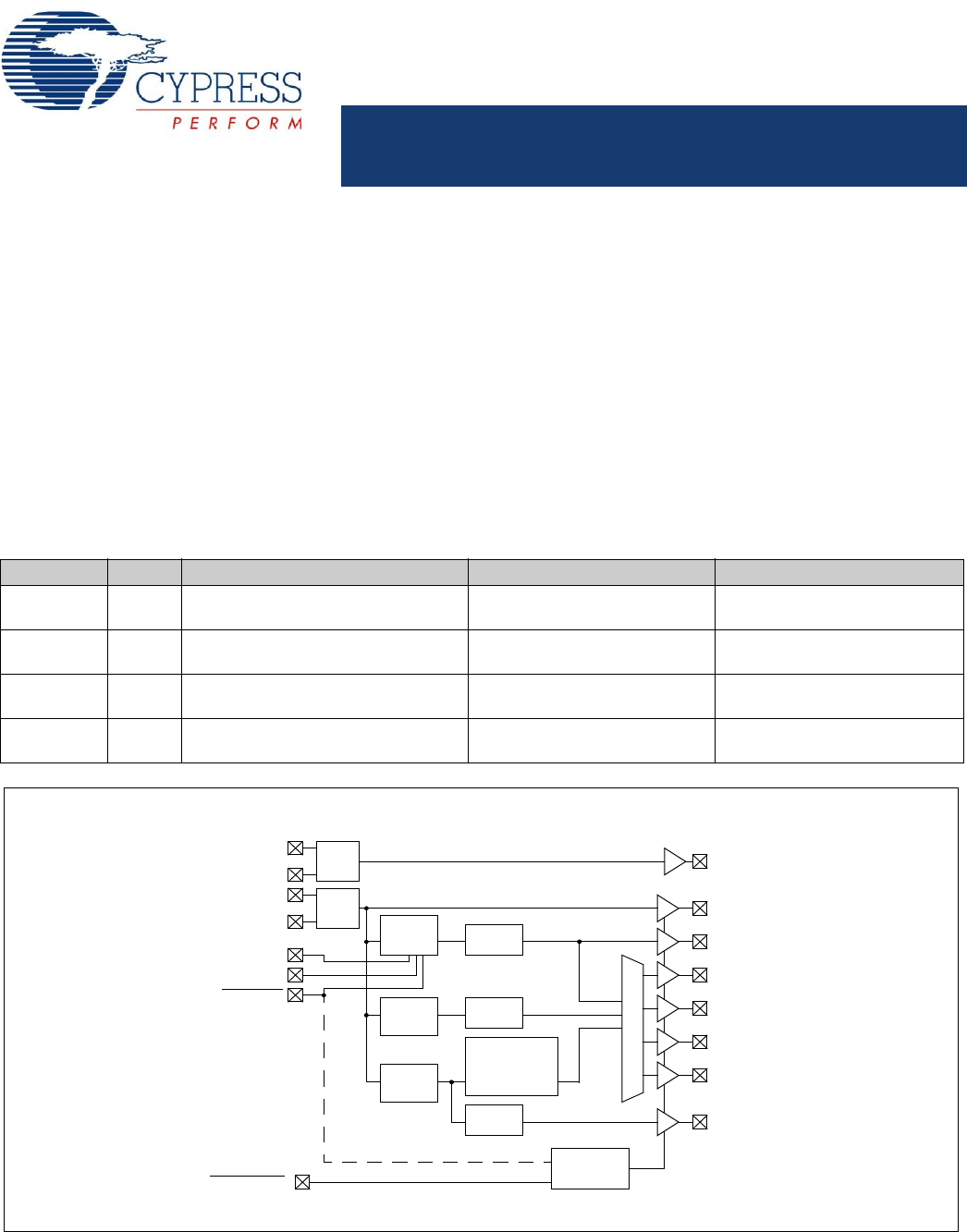

Logic Block Diagram

32XIN

32XOUT

XTALIN

XTALOUT

S2/SUSPEND

S1

S0

SHUTDOWN

/

32K

CONFIG

EPROM

OSC.

XBUF

CPLL

SPLL

UPLL

OSC.

CPUCLK

CLKA

CLKB

CLKC

CLKD

MUX

OE

CLKF

/1,2,4

/1,2,3,4,5,6

/8,10,12,13

/20,24,26,40

/48,52,96,104

/2,3,4

/1,2,4,8

(8 BIT)

(8 BIT)

(10 BIT)

[+] Feedback