CY2291

Document #: 38-07189 Rev. *C Page 9 of 12

t

6

Output Enable

Time

Time for output to leave three-state mode after

SHUTDOWN

/OE goes HIGH

10 15 ns

t

7

Skew

Skew delay between any identical or related outputs

[3,

12, 15]

< 0.25 0.5 ns

t

8

CPUCLK Slew Frequency transition rate 1.0 20.0 MHz/ms

t

9A

Clock Jitter

[14]

Peak-to-peak period jitter (t

9A

Max. – t

9A

min.),% of

clock period (f

OUT

< 4 MHz)

< 0.5 1 %

t

9B

Clock Jitter

[14]

Peak-to-peak period jitter (t

9B

Max. – t

9B

min.) (4 MHz

<

f

OUT

< 16 MHz)

< 0.7 1 ns

t

9C

Clock Jitter

[14]

Peak-to-peak period jitter

(16 MHz < f

OUT

<

50 MHz)

< 400 500 ps

t

9D

Clock Jitter

[14]

Peak-to-peak period jitter (f

OUT

> 50 MHz) < 250 350 ps

t

10A

Lock Time for

CPLL

Lock Time from Power Up < 25 50 ms

t

10B

Lock Time for

UPLL and SPLL

Lock Time from Power Up < 0.25 1 ms

Slew Limits CPU PLL Slew Limits CY2291I 8 66.6 MHz

CY2291FI 8 60 MHz

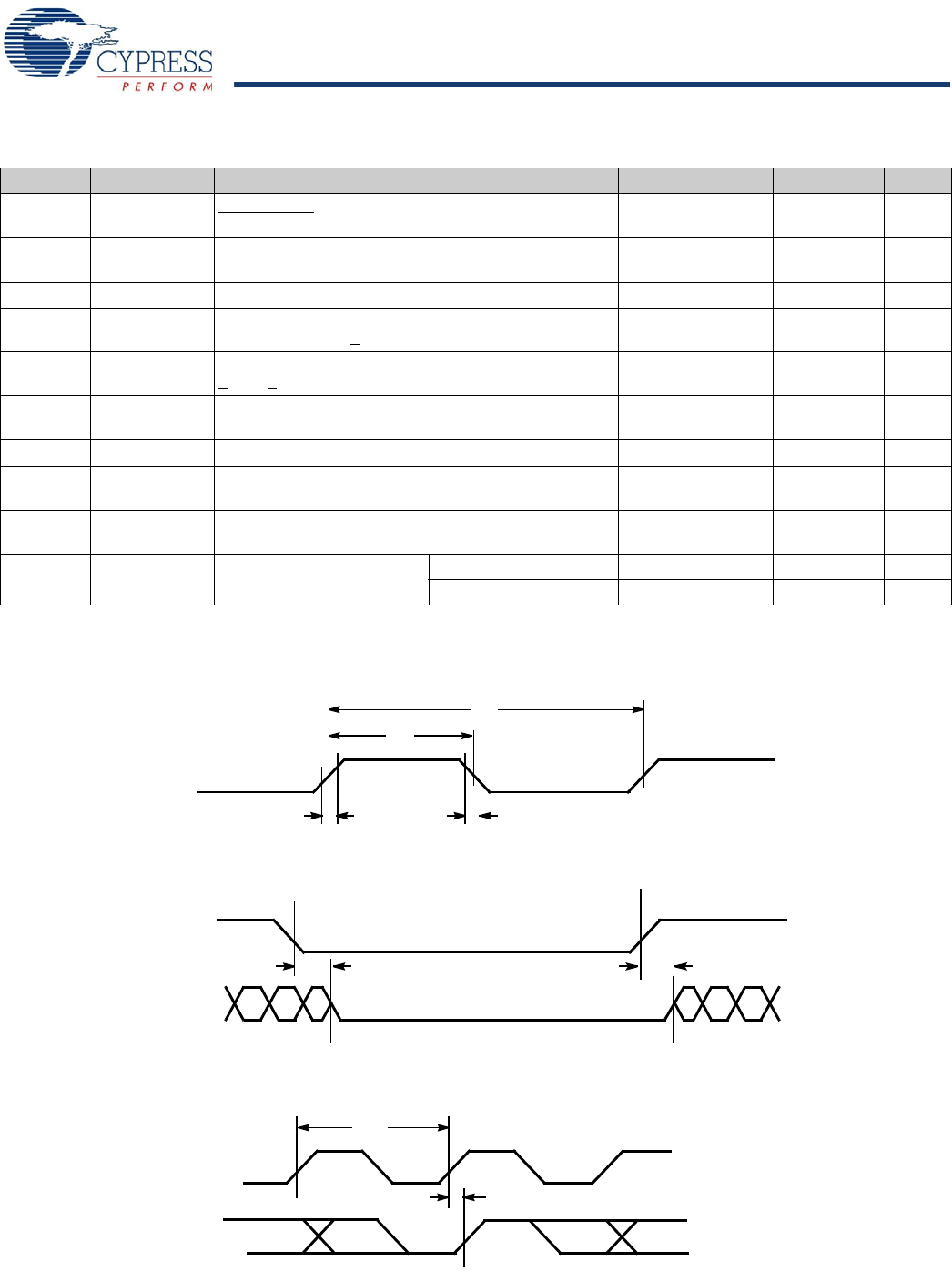

Switching Waveforms

Switching Characteristics, Industrial 3.3V (continued)

Parameter Name Description Min. Typ. Max. Unit

t

1

OUTPUT

t

2

t

3

t

4

Figure 2. All Outputs, Duty Cycle and Rise/Fall Time

Figure 3. Output Three-State Timing

[4]

t

5

OE

ALL

THREE-STATE

OUTPUTS

t

6

t

7

CLK

OUTPUT

RELATED

CLK

t

9A

Figure 4. CLK Outputs Jitter and Skew

[+] Feedback