CY2291

Document #: 38-07189 Rev. *C Page 2 of 12

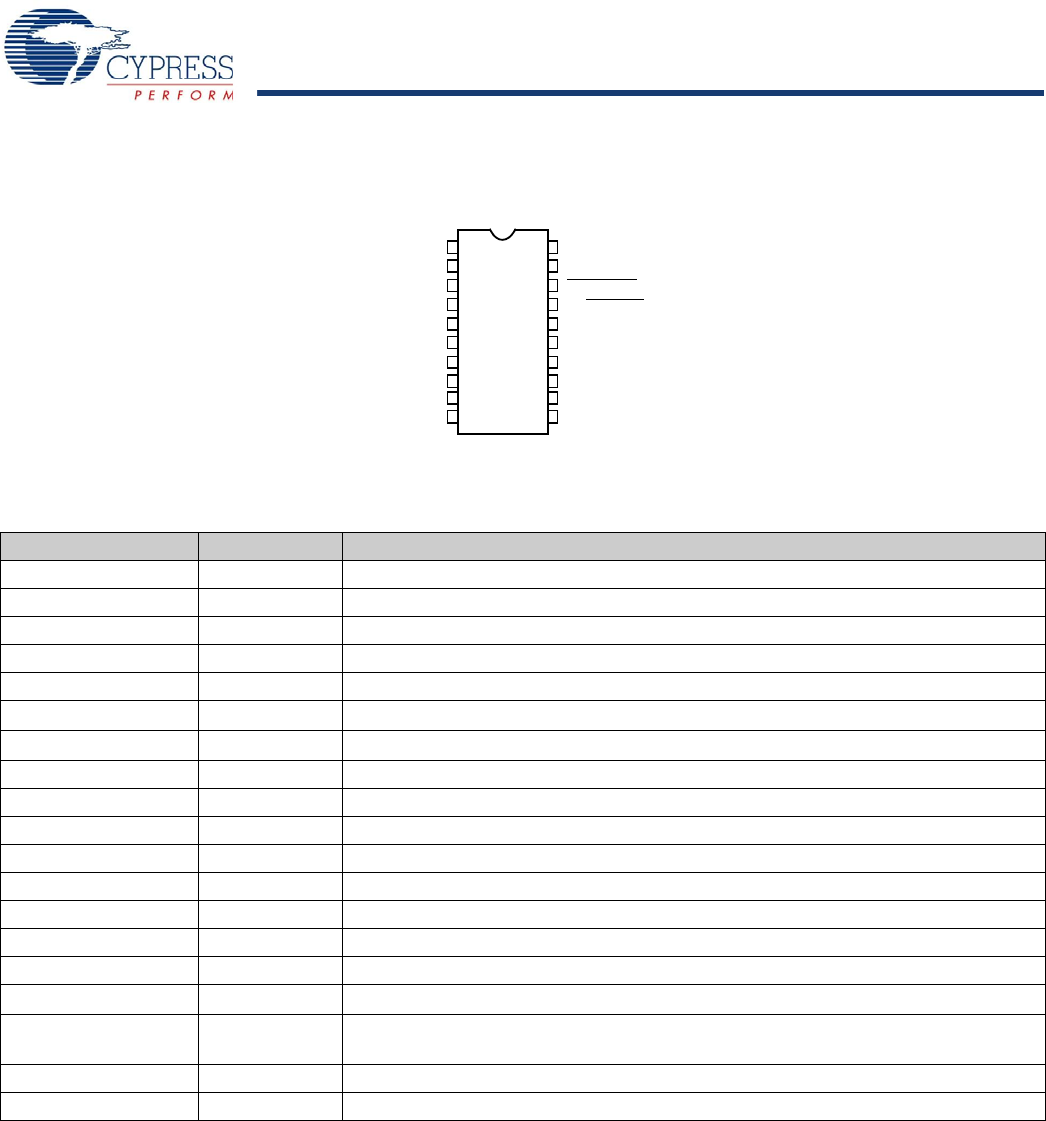

Pinouts

Figure 1. CY2291- 20-pin SOIC

Pin Definitions

Name Pin Number Description

32XOUT 1 32.768-kHz crystal feedback.

32K 2 32.768-kHz output (always active if VBATT is present).

CLKC 3 Configurable clock output C.

VDD 4, 16 Voltage supply.

GND 5 Ground.

XTALIN

[1]

6

Reference crystal input or external reference clock input.

XTALOUT

[1, 2]

7

Reference crystal feedback.

XBUF 8 Buffered reference clock output.

CLKD 9 Configurable clock output D.

CPUCLK 10 CPU frequency clock output.

CLKB 11 Configurable clock output B.

CLKA 12 Configurable clock output A.

CLKF 13 Configurable clock output F.

S0 14 CPU clock select input, bit 0.

S1 15 CPU clock select input, bit 1.

S2/SUSPEND 17

CPU clock select input, bit 2. Optionally enables suspend feature when LOW.

[3]

SHUTDOWN/OE 18

Places outputs in three-state

[4]

condition and shuts down chip when LOW. Optionally, only

places outputs in three-state

[4]

condition and does not shut down chip when LOW.

VBATT 19 Battery supply for 32.768-kHz circuit.

32XIN 20 32.768-kHz crystal input.

CLKB

1

2

3

4

5

6

7

8

9

10

11

12

13

14

32XOUT

32K

CLKC

V

DD

GND

XTALIN

XTALOUT

XBUF

32XIN

V

BATT

SHUTDOWN/OE

S2/SUSPEND

V

DD

S1

S0

CLKF

15

16

17

18

19

20

CLKD

CPUCLK

CLKA

Notes

1. For best accuracy, use a parallel-resonant crystal, C

LOAD

≈ 17 pF or 18 pF.

2. Float XTALOUT pin if XTALIN is driven by reference clock (as opposed to crystal).

3. Please refer to application note “Understanding the CY2291, CY2292 and CY2295” for more information.

4. The CY2291 has weak pull downs on all outputs (except 32K). Hence, when a three-state condition is forced on the outputs, the output pins are pulled LOW.

[+] Feedback