CY24272

Document Number: 001-42414 Rev. ** Page 9 of 13

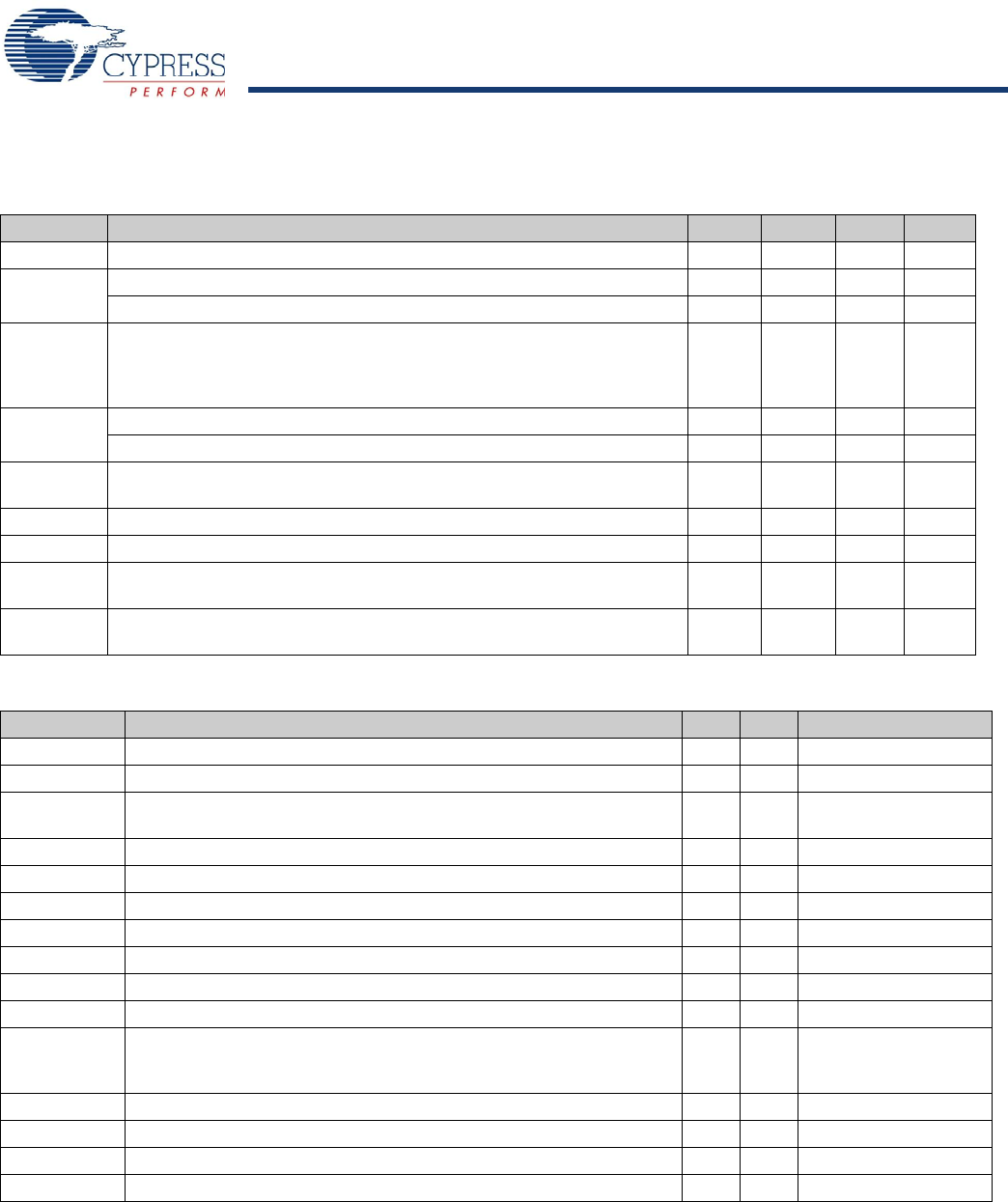

AC Electrical Specification

The AC Electrical specifications follow.

[6]

Parameter Description Min Typ Max Unit

t

CYCLE

Clock Cycle time

[19]

1.25 3.34 ns

t

JIT(cc)

Jitter over 1-6 clock cycles at 400–635 MHz

[20]

–2540ps

Jitter over 1-6 clock cycles at 638–667 MHz – 25 30 ps

L

20

Phase noise SSB spectral purity L(f) at 20 MHz offset: 400–500 MHz

(In addition, device must not exceed L(f) = 10log[1+(50x10

6

/f)

2.4

] –138 for

f = 1 MHz to 100 MHz except for the region near f = REFCLK/Q where Q is

the value of the internal reference divider.)

– –135 –128 dBC/Hz

t

JIT(hper,cc)

Cycle-to-cycle duty cycle error at 400–635 MHz – 25 40 ps

Cycle-to-cycle duty cycle error at 636–667 MHz – 25 30 ps

Δt

SKEW

Drift in t

SKEW

when ambient temperature varies between 0°C and 70°C and

supply voltage varies between 2.375V and 2.625V.

[21]

––15ps

DC Long term average output duty cycle 45% 50 55% t

CYCLE

t

EER,SCC

PLL output phase error when tracking SSC –100 – 100 ps

t

CR

,t

CF

Output rise and fall times at 400–667 MHz (measured at 20%–80% of output

voltage)

–150–ps

t

CR,CF

Difference between output rise and fall times on the same pin of the single

device (20%–80%) of 400–667 MHz

[22]

– – 100 ps

Table 9. SMBus Timing Specification

Parameter Description Min Max Units

FSMB SMBus Operating Frequency 10 100 kHz

TBUF Bus free time between Stop and Start Condition 4.7 μs

THD:STA Hold time after (Repeated) Start Condition.

After this period, the first clock is generated.

4.0 μs

TSU:STA Repeated Start Condition setup time 4.7 μs

TSU:STO Stop Condition setup time 4.0 μs

THD:DAT Data Hold time 0 ns

TSU:DAT Data Setup time 250 ns

TTIMEOUT Detect clock low timeout Not supported

TLOW Clock low period 4.7 μs

THIGH Clock high period 4.0 50 μs

TLOW:SEXT Cumulative clock low extend time (slave device) 25 ms

CY24272 doesn’t

extend

TLOW:MEXT Cumulative clock low extend time (master device) 10 ms

TF Clock/Data Fall Time 300 ns

TR Clock/Data Rise Time 1000 ns

TPOR Time in which a device must be operational after power on reset 500 ms

[+] Feedback