CY62128EV30

Document #: 38-05579 Rev. *D Page 3 of 11

Maximum Ratings

Exceeding maximum ratings may impair the useful life of the

device. These user guidelines are not tested.

Storage Temperature.................................. –65°C to +150°C

Ambient Temperature with

Power Applied ............................................ –55°C to +125°C

Supply Voltage to Ground

Potential..........................................–0.3V to V

CC(max)

+ 0.3V

DC Voltage Applied to Outputs

in High-Z State

[4, 5]

.........................–0.3V to V

CC(max)

+ 0.3V

DC Input Voltage

[4,5]

.......................–0.3V to V

CC(max)

+ 0.3V

Output Current into Outputs (LOW)............................. 20 mA

Static Discharge Voltage.......................................... > 2001V

(MIL-STD-883, Method 3015)

Latch up Current.....................................................> 200 mA

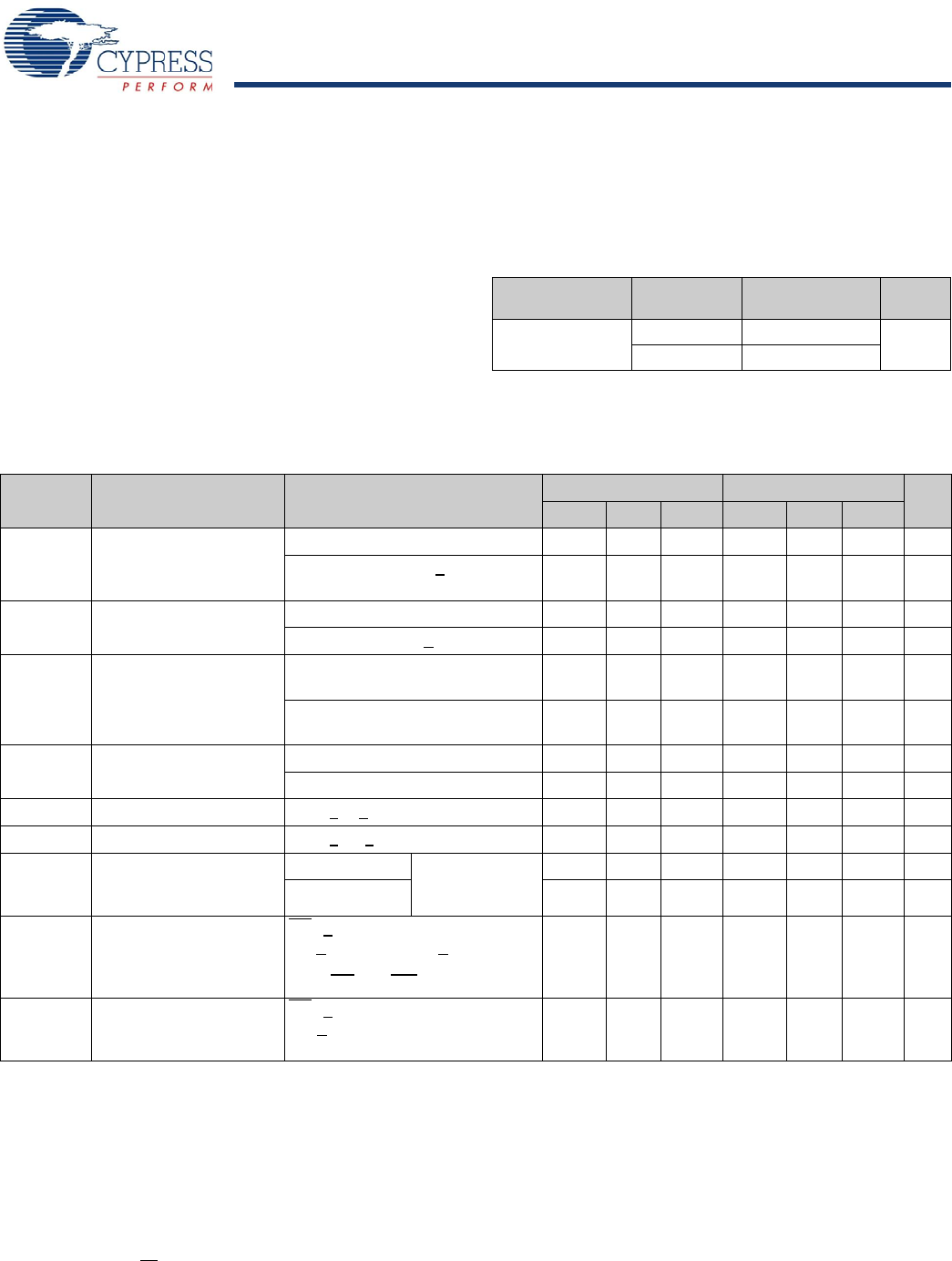

Operating Range

Device Range

Ambient

Temperature

V

CC

[6]

CY62128EV30LL Ind’l/Auto-A –40°C to +85°C 2.2V to

3.6V

Auto-E –40°C to +125°C

Electrical Characteristics

(Over the Operating Range)

Parameter Description Test Conditions

45 ns (Ind’l/Auto-A) 55 ns (Auto-E)

Unit

Min Typ

[3]

Max Min Typ

[3]

Max

V

OH

Output HIGH Voltage I

OH

= –0.1 mA 2.0 2.0 V

I

OH

= –1.0 mA, V

CC

> 2.70V

2.4 2.4 V

V

OL

Output LOW Voltage I

OL

= 0.1 mA 0.4 0.4 V

I

OL

= 2.1 mA, V

CC

> 2.70V 0.4 0.4 V

V

IH

Input HIGH Voltage V

CC

= 2.2V to 2.7V 1.8 V

CC

+

0.3V

1.8 V

CC

+

0.3V

V

V

CC

= 2.7V to 3.6V 2.2 V

CC

+

0.3V

2.2 V

CC

+

0.3V

V

V

IL

Input LOW Voltage V

CC

= 2.2V to 2.7V –0.3 0.6 –0.3 0.6 V

V

CC

= 2.7V to 3.6V –0.3 0.8 –0.3 0.8 V

I

IX

Input Leakage Current GND < V

I

< V

CC

–1 +1 –4 +4 μA

I

OZ

Output Leakage Current GND < V

O

< V

CC

, Output Disabled –1 +1 –4 +4 μA

I

CC

V

CC

Operating Supply

Current

f = f

max

= 1/t

RC

V

CC

= V

CCmax

I

OUT

= 0 mA

CMOS levels

11 16 11 35 mA

f = 1 MHz 1.3 2.0 1.3 4.0 mA

I

SB1

Automatic CE

Power down

Current — CMOS Inputs

CE

1

> V

CC

−0.2V, CE

2

< 0.2V

V

IN

> V

CC

–0.2V, V

IN

< 0.2V)

f = f

max

(Address and Data Only),

f = 0 (OE

and WE), V

CC

= 3.60V

14 135μA

I

SB2

[7]

Automatic CE

Power down

Current — CMOS Inputs

CE

1

> V

CC

– 0.2V, CE

2

< 0.2V

V

IN

> V

CC

– 0.2V or V

IN

< 0.2V,

f = 0, V

CC

= 3.60V

14 130μA

Notes

4. V

IL(min)

= –2.0V for pulse durations less than 20 ns.

5. V

IH(max)

= V

CC

+0.75V for pulse durations less than 20 ns.

6. Full device AC operation assumes a 100 μs ramp time from 0 to V

CC

(min) and 200 μs wait time after V

CC

stabilization.

7. Only chip enables (CE

1

and CE

2

) must be at CMOS level to meet the I

SB2

/ I

CCDR

spec. Other inputs can be left floating.

[+] Feedback