PRELIMINARY

CY7C1330AV25

CY7C1332AV25

Document No: 001-07844 Rev. *A Page 16 of 19

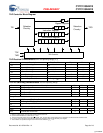

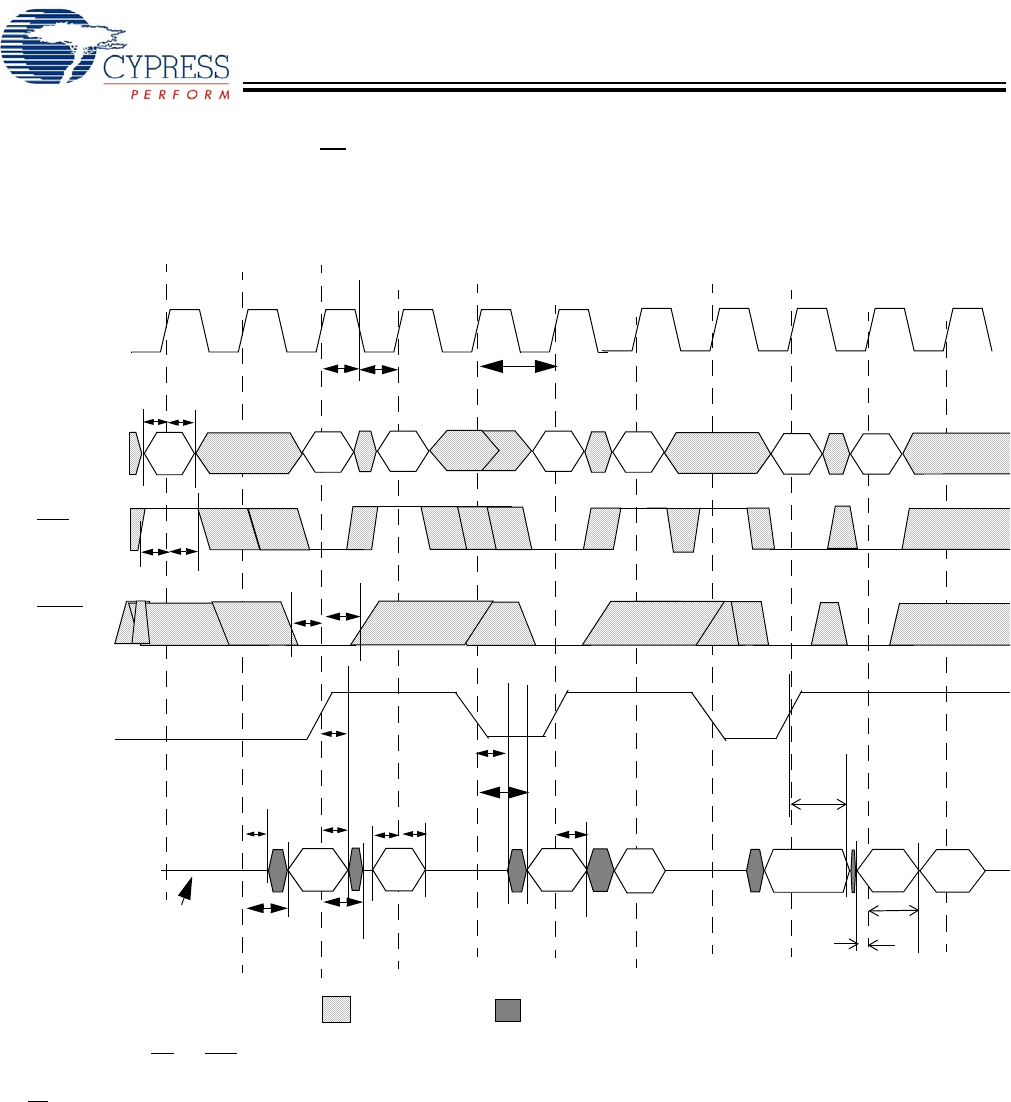

Switching Waveforms

READ/WRITE/DESELECT Sequence (OE Controlled)

[23, 24, 25, 26]

Notes:

23.The combination of WE

and BWS

x

(x = a, b, c, d for x36 and x = a, b for x18) define a write cycle (see Write Cycle Description table).

24.All chip enables need to be active in order to select the device. Any chip enable can deselect the device.

25.RAx stands for Read Address X, WAx Write Address X, Dx stands for Data-in for location X, Qx stands for Data-out for location X.

26.CE

held LOW.

K

ADDRESS

WE

Data

In/Out

t

CYC

t

CH

t

CL

RA1

t

AH

t

AS

t

WES

t

WEH

t

CO

Q1

= DON’T CARE

= UNDEFINED

Out

D2

In

READ

WRITE

READ

DESELECT

WRITE

READ

READ

WRITE

WRITE

DESELECT

WA2

WA5

RA6

t

CLZ

t

DOH

Q3

Out

t

CHZ

Device

originally

deselected

D7

In

t

DOH

Q6

Out

t

DS

t

DH

RA3

D5

In

WA7

WA8

D8

In

OE/

t

EOHZ

t

EOLZ

t

EOV

t

EOHZ

t

DS

t

DH

BWS

x

t

WES

t

WEH

DESELECT

[+] Feedback