CY7C1347G

Document #: 38-05516 Rev. *F Page 9 of 22

Maximum Ratings

Exceeding the maximum ratings may shorten the battery life of

the device. User guidelines are not tested.

Storage Temperature .....................................−65°C to +150°C

Ambient Temperature with

Power Applied..................................................−55°C to +125°C

Supply Voltage on V

DD

Relative to GND.........−0.5V to +4.6V

Supply Voltage on V

DDQ

Relative to GND........−0.5V to +V

DD

DC Voltage Applied to Outputs

in High-Z State........................................... −0.5V to V

DD

+ 0.5V

DC Input Voltage .......................................−0.5V to V

DD

+ 0.5V

Current into Outputs (LOW).........................................20 mA

Static Discharge Voltage.......................................... > 2001V

(MIL-STD-883, Method 3015)

Latch-Up Current................................................... > 200 mA

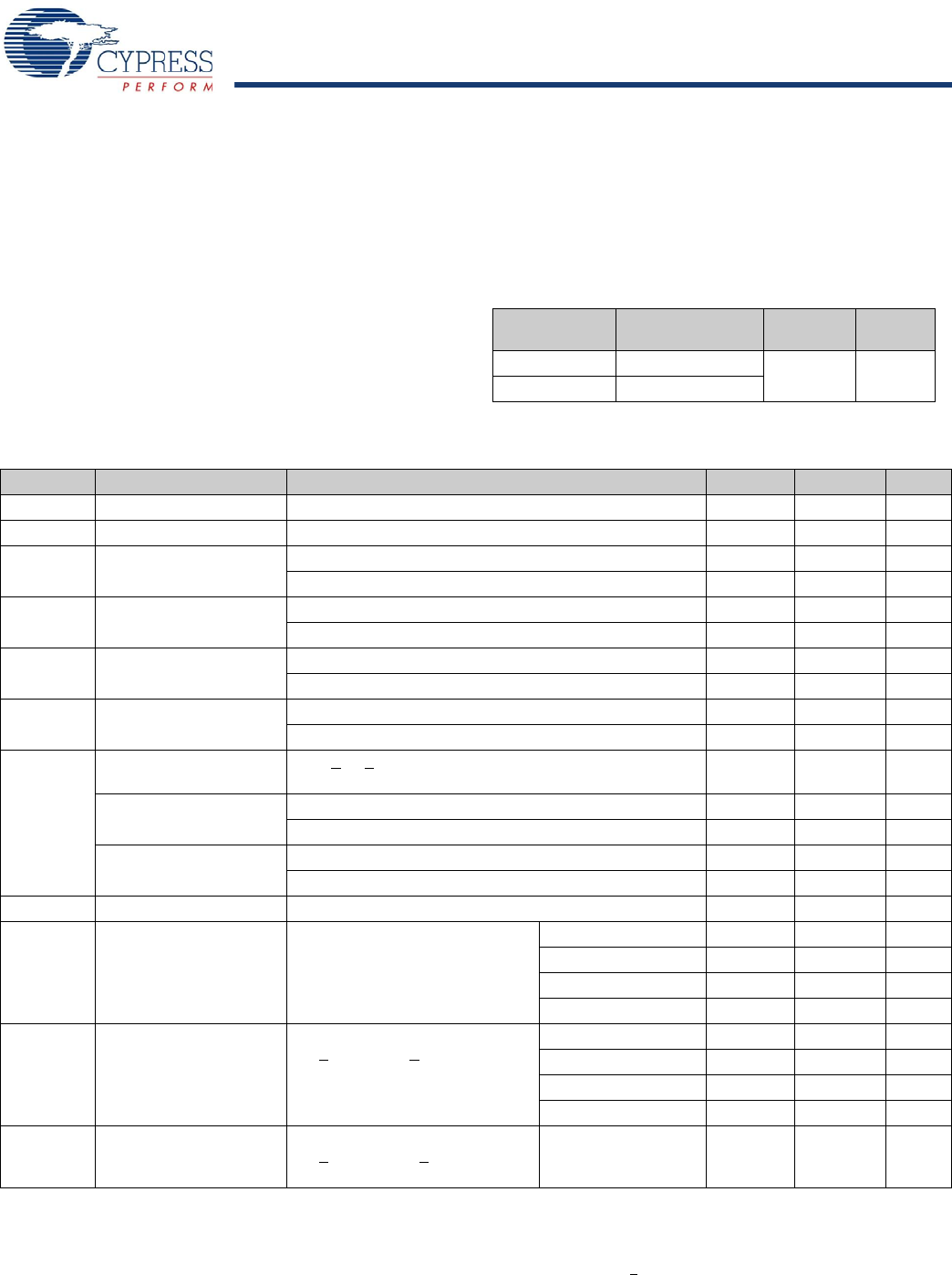

Operating Range

Range

Ambient

Temperature

V

DD

V

DDQ

Commercial 0°C to +70°C 3.3V

−5%/+10%

2.5V −5%

to V

DD

Industrial –40°C to +85°C

Electrical Characteristics

Over the Operating Range

[8, 9]

Parameter Description Test Conditions Min Max Unit

V

DD

Power Supply Voltage 3.135 3.6 V

V

DDQ

IO Supply Voltage 2.375 V

DD

V

V

OH

Output HIGH Voltage For 3.3V IO, I

OH

= –4.0 mA 2.4 V

For 2.5V IO, I

OH

= –1.0 mA 2.0 V

V

OL

Output LOW Voltage For 3.3V IO, I

OL

= 8.0 mA 0.4 V

For 2.5V IO, I

OL

= 1.0 mA 0.4 V

V

IH

Input HIGH Voltage

[8]

For 3.3V IO 2.0 V

DD

+ 0.3V V

For 2.5V IO 1.7 V

DD

+ 0.3V V

V

IL

Input LOW Voltage

[8]

For 3.3V IO –0.3 0.8 V

For 2.5V IO –0.3 0.7 V

I

X

Input Leakage Current

Except ZZ and MODE

GND < V

I

< V

DDQ

−55μA

Input Current of MODE Input = V

SS

−30 μA

Input = V

DD

5 μA

Input Current of ZZ Input = V

SS

−5 μA

Input = V

DD

30 μA

I

OZ

Output Leakage Current GND ≤ V

I

≤ V

DDQ,

Output Disabled −55μA

I

DD

V

DD

Operating Supply

Current

V

DD

= Max., I

OUT

= 0 mA,

f = f

MAX

= 1/t

CYC

4 ns cycle, 250 MHz 325 mA

5 ns cycle, 200 MHz 265 mA

6 ns cycle, 166 MHz 240 mA

7.5 ns cycle, 133 MHz 225 mA

I

SB1

Automatic CE

Power Down

Current—TTL Inputs

Max. V

DD

, Device Deselected,

V

IN

> V

IH

or V

IN

< V

IL

f = f

MAX

= 1/t

CYC

4 ns cycle, 250 MHz 120 mA

5 ns cycle, 200 MHz 110 mA

6 ns cycle, 166 MHz 100 mA

7.5 ns cycle, 133 MHz 90 mA

I

SB2

Automatic CE

Power Down

Current—CMOS Inputs

Max. V

DD

, Device Deselected,

V

IN

< 0.3V or V

IN

> V

DDQ

– 0.3V,

f = 0

All speeds 40 mA

Notes

8. Overshoot: V

IH

(AC) < V

DD

+1.5V (pulse width less than t

CYC

/2). Undershoot: V

IL

(AC) > –2V (pulse width less than t

CYC

/2).

9. T

Power up

: assumes a linear ramp from 0V to V

DD

(min) within 200 ms. During this time V

IH

< V

DD

and V

DDQ

< V

DD

.

[+] Feedback