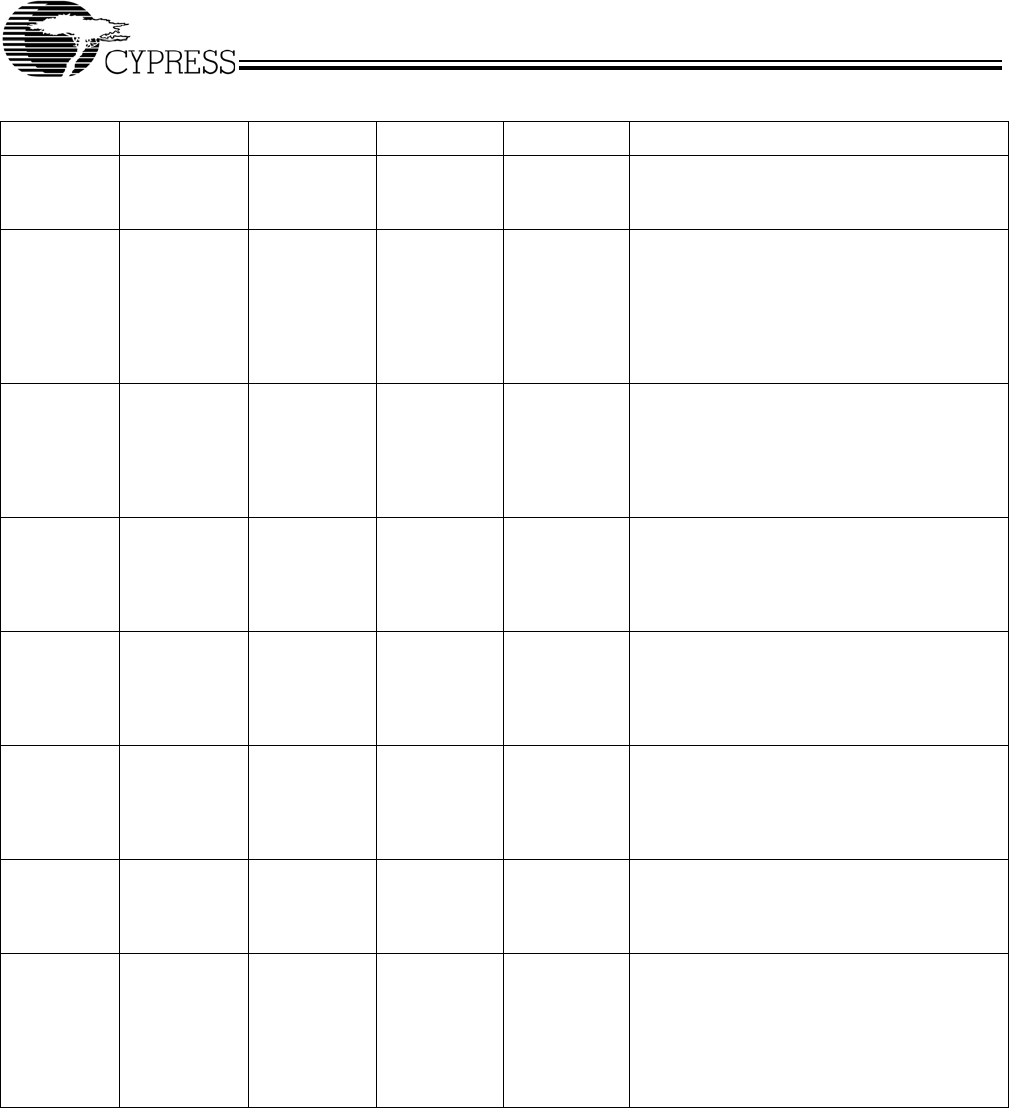

CY7C1380C

CY7C1382C

Document #: 38-05237 Rev. *D Page 8 of 36

V

SSQ

5,10,21,26,55,

60,71,

76

- - I/O Ground Ground for the I/O circuitry.

V

DDQ

4,11,20,27,54,

61,70,

77

A1,F1,J1,M1,

U1,

A7,F7,J7,M7,

U7

C3,C9,D3,D9,

E3,E9,F3,F9,G

3,

G9,J3,J9,

K3,K9,L3,

L9,M3,M9,N3,

N9

I/O Power

Supply

Power supply for the I/O circuitry.

MODE 31 R3 R1 Input-

Static

Selects Burst Order. When tied to GND

selects linear burst sequence. When tied to V

DD

or left floating selects interleaved burst

sequence. This is a strap pin and should remain

static during device operation. Mode Pin has an

internal pull-up.

TDO - U5 P7 JTAG serial

output

Synchronous

Serial data-out to the JTAG circuit. Delivers

data on the negative edge of TCK. If the JTAG

feature is not being utilized, this pin should be

disconnected. This pin is not available on TQFP

packages.

TDI - U3 P5 JTAG serial

input

Synchronous

Serial data-In to the JTAG circuit. Sampled

on the rising edge of TCK. If the JTAG feature

is not being utilized, this pin can be discon-

nected or connected to V

DD

. This pin is not

available on TQFP packages.

TMS - U2 R5 JTAG serial

input

Synchronous

Serial data-In to the JTAG circuit. Sampled

on the rising edge of TCK. If the JTAG feature

is not being utilized, this pin can be discon-

nected or connected to V

DD

. This pin is not

available on TQFP packages.

TCK - U4 R7 JTAG-Clock Clock input to the JTAG circuitry. If the JTAG

feature is not being utilized, this pin must be

connected to V

SS

. This pin is not available on

TQFP packages.

NC 14,16,66,

39,38

B1,C1,

R1,T1,T2,J3,

D4,

L4,J5,R5,6T,

6U,

B7,C7,

R7

A11,B1,C2,C1

0,H1,H3,H9,

H10,

N2,N5,N7,N10

,P1,A1,B11,P2

,R2,N6

- No Connects. Not internally connected to the

die

CY7C1380C–Pin Definitions (continued)

Name TQFP BGA fBGA I/O Description

[+] Feedback