CY8C20x36/46/66, CY8C20396

Document Number: 001-12696 Rev. *D Page 22 of 34

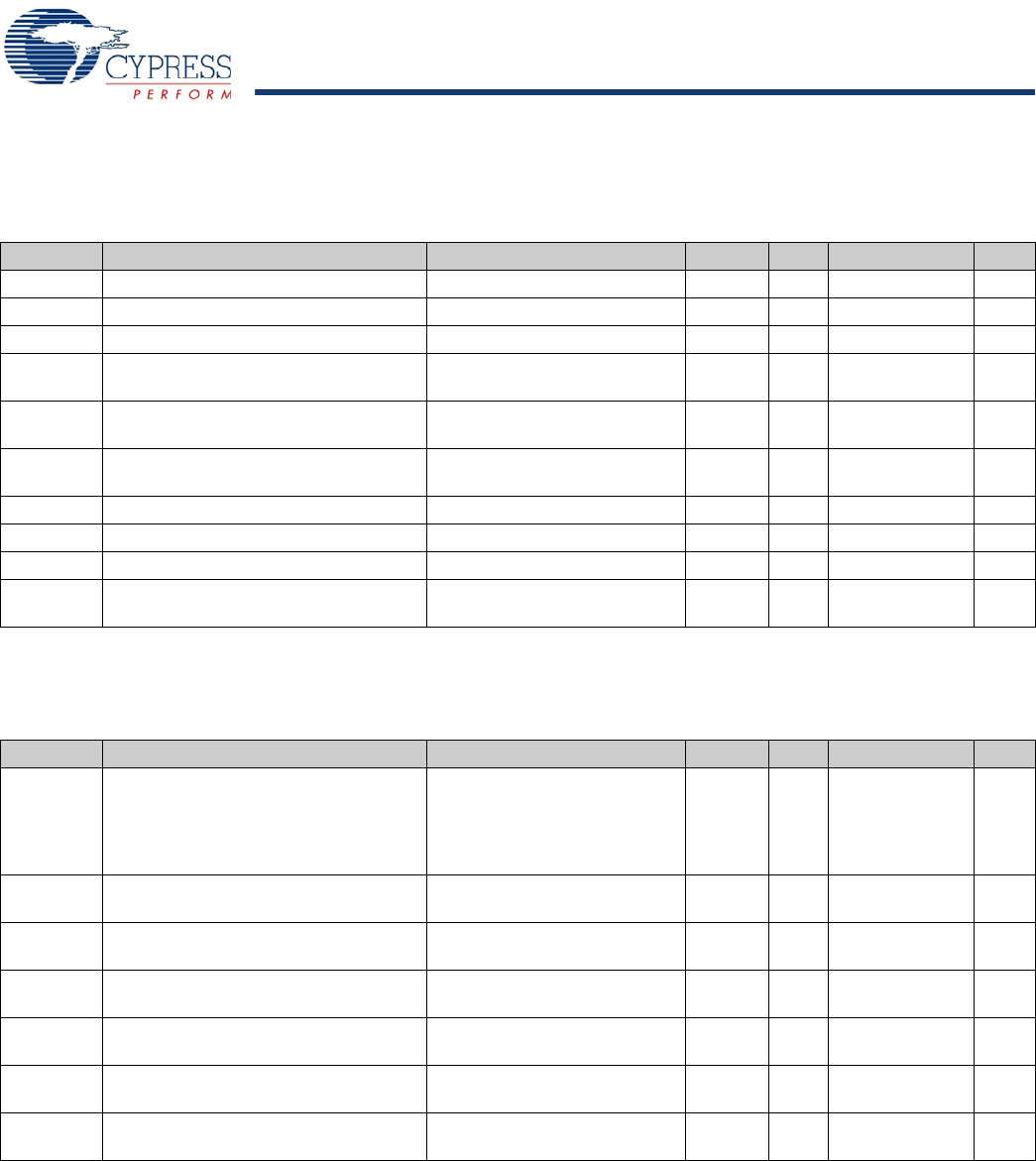

AC Chip-Level Specifications

The following table lists guaranteed maximum and minimum specifications for the entire voltage and temperature ranges.

AC General Purpose IO Specifications

The following table lists guaranteed maximum and minimum specifications for the entire voltage and temperature ranges.

Table 23. AC Chip-Level Specifications

Symbol Description Conditions Min Typ Max Units

F

MAX

Maximum Operating Frequency 24 – – MHz

F

CPU

Maximum Processing Frequency 24 – – MHz

F

32K1

Internal Low Speed Oscillator Frequency 19 32 50 kHz

F

IMO24

Internal Main Oscillator Frequency at 24

MHz Setting

22.8 24 25.2 MHz

F

IMO12

Internal Main Oscillator Frequency at 12

MHz Setting

11.4 12 12.6 MHz

F

IMO6

Internal Main Oscillator Frequency at 6

MHz Setting

5.7 6.0 6.3 MHz

DC

IMO

Duty Cycle of IMO 40 50 60 %

T

RAMP

Supply Ramp Time 0 – – μs

T

XRST

External Reset Pulse Width at Power Up After supply voltage is valid 1 ms

T

XRST2

External Reset Pulse Width after Power

Up

Applies after part has booted 10 μs

Table 24. AC GPIO Specifications

Symbol Description Conditions Min Typ Max Units

F

GPIO

GPIO Operating Frequency Normal Strong Mode Port 0, 1 0

0

–

–

6 MHz for

1.71V<Vdd<2.4V

12 MHz for

2.4V<Vdd<5.5V

MHz

TRise23 Rise Time, Strong Mode, Cload = 50 pF

Ports 2 or 3

Vdd = 3.0 to 3.6V, 10% – 90% 15 – 80 ns

TRise23L Rise Time, Strong Mode Low Supply,

Cload = 50 pF, Ports 2 or 3

Vdd = 1.71 to 3.0V, 10% – 90% 15 – 80 ns

TRise01 Rise Time, Strong Mode, Cload = 50 pF

Ports 0 or 1

Vdd = 3.0 to 3.6V, 10% – 90%

LDO enabled or disabled

10 – 50 ns

TRise01L Rise Time, Strong Mode Low Supply,

Cload = 50 pF, Ports 0 or 1

Vdd = 1.71 to 3.0V, 10% – 90%

LDO enabled or disabled

10 – 80 ns

TFall Fall Time, Strong Mode, Cload = 50 pF

All Ports

Vdd = 3.0 to 3.6V, 10% – 90% 10 – 50 ns

TFallL Fall Time, Strong Mode Low Supply,

Cload = 50 pF, All Ports

Vdd = 1.71 to 3.0V, 10% – 90% 10 – 70 ns

[+] Feedback