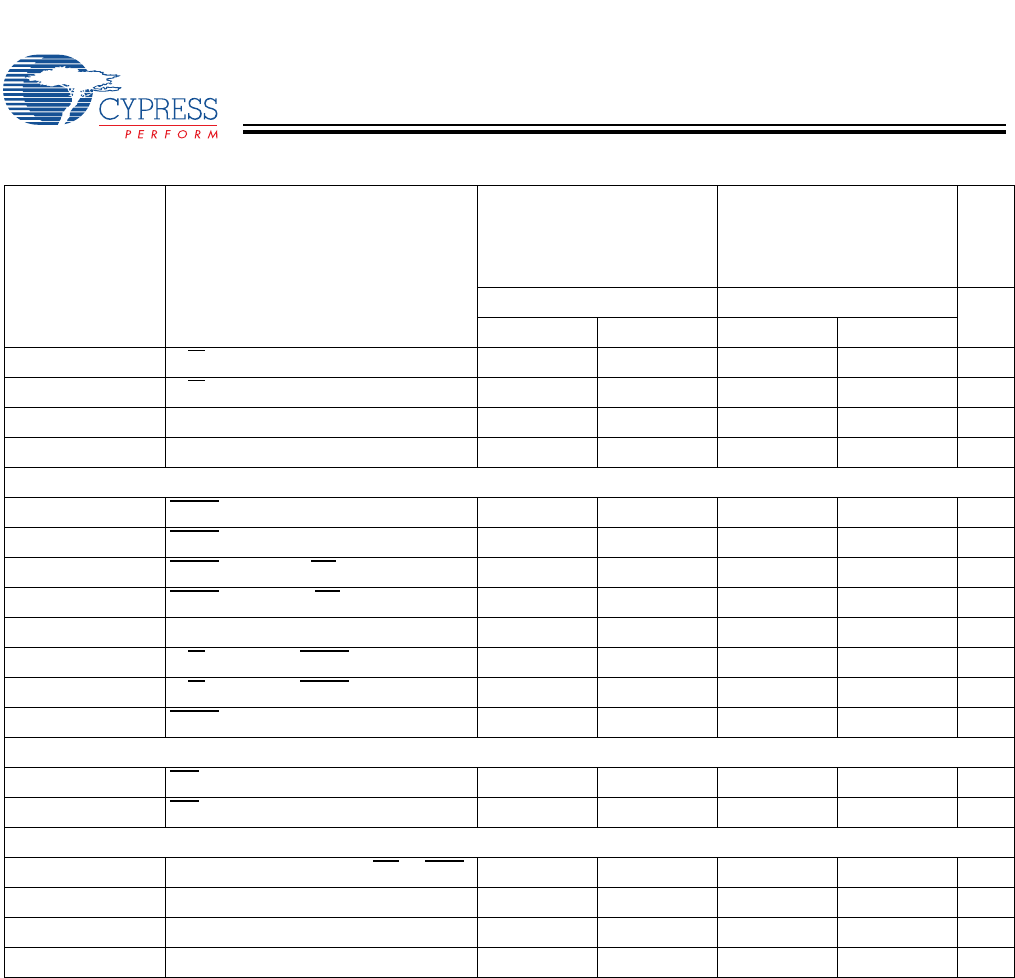

CYDC256B16, CYDC128B16,

CYDC064B16, CYDC128B08,

CYDC064B08

Document #: 001-01638 Rev. *E Page 17 of 26

t

HZWE

[30, 31]

R/W LOW to High Z 15 25 ns

t

LZWE

[30, 31]

R/W HIGH to Low Z 0 0 ns

t

WDD

[32]

Write Pulse to Data Delay 55 80 ns

t

DDD

[32]

Write Data Valid to Read Data Valid 55 80 ns

Busy Timing

[33]

t

BLA

BUSY LOW from Address Match 30 45 ns

t

BHA

BUSY HIGH from Address Mismatch 30 45 ns

t

BLC

BUSY LOW from CE LOW 30 45 ns

t

BHC

BUSY HIGH from CE HIGH 30 45 ns

t

PS

[34]

Port Set-up for Priority 5 5 ns

t

WB

R/W HIGH after BUSY (Slave) 0 0 ns

t

WH

R/W HIGH after BUSY HIGH (Slave) 20 35 ns

t

BDD

[35]

BUSY HIGH to Data Valid 30 40 ns

Interrupt Timing

[33]

t

INS

INT Set Time 35 45 ns

t

INR

INT Reset Time 35 45 ns

Semaphore Timing

t

SOP

SEM Flag Update Pulse (OE or SEM)10 15 ns

t

SWRD

SEM Flag Write to Read Time 10 10 ns

t

SPS

SEM Flag Contention Window 10 10 ns

t

SAA

SEM Address Access Time 40 55 ns

Switching Characteristics for V

CC

= 3.0V Over the Operating Range (continued)

Parameter Description

CYDC256B16,

CYDC128B16,

CYDC064B16,

CYDC128B08,

CYDC064B08

CYDC256B16,

CYDC128B16,

CYDC064B16,

CYDC128B08,

CYDC064B08 Unit

-40 -55

Min. Max. Min. Max.

[+] Feedback