Chapter 3 Programming

IPMC7126E/7616E I/O Module Installation and Use (6806800A45B)

19

MVME6100

The MVME6100 IPMC module PCI arbitration is performed by the MV64360 ASIC. The internal

PCI arbiter REQ#/GNT# signals are multiplexed on the MV64360 MPP[31:0] pins. The internal

PCI arbiter is disabled by default (the MPP pins function as general purpose inputs). Software

will configure the MPP pins to function as request/grant pairs for the internal PCI arbiter.

The IPMC module arbitration pairs for the MVME6100 are assigned to the MPP pins as follows;

■ MPP pin 8, PCI Bus Grant (PIB device on IPMC module)

■ MPP pin 9, PCI Bus Request (PIB device on IPMC module)

■ MPP pin 12, PCI Bus Grant (SCSI device on IPMC module)

■ MPP pin 13, PCI Bus Request (SCSI device on IPMC module)

Interrupt Assignments

The interrupt architecture for the IPMC712 and IPMC761 is fully compliant with the PowerPlusII

Programming Specification for a single processor board configuration.

MVME5100 IPMC Module Interrupt Assignments

Legacy interrupt assignment for the PCI-to-ISA Bridge (PIB) is maintained to ensure software

compatibility between MVME5100 and IPMC761 while in IPMC mode. This is accomplished by

using the on-board IPMC761 connector to route the PIB’s interrupt to external interrupt 0 of the

Hawk’s MPIC.

The MVME5100 Ethernet port 2 is routed to the PIB’s IRQ10 input. The SCSI interrupt on the

IPMC761 is also routed to the PIB at IRQ14. The SCSI device is connected to the INTA# pin

J11-04 of PMC Slot 1. Interrupts are routed to the Hawk from on-board resources as specified

by the module’s programming.

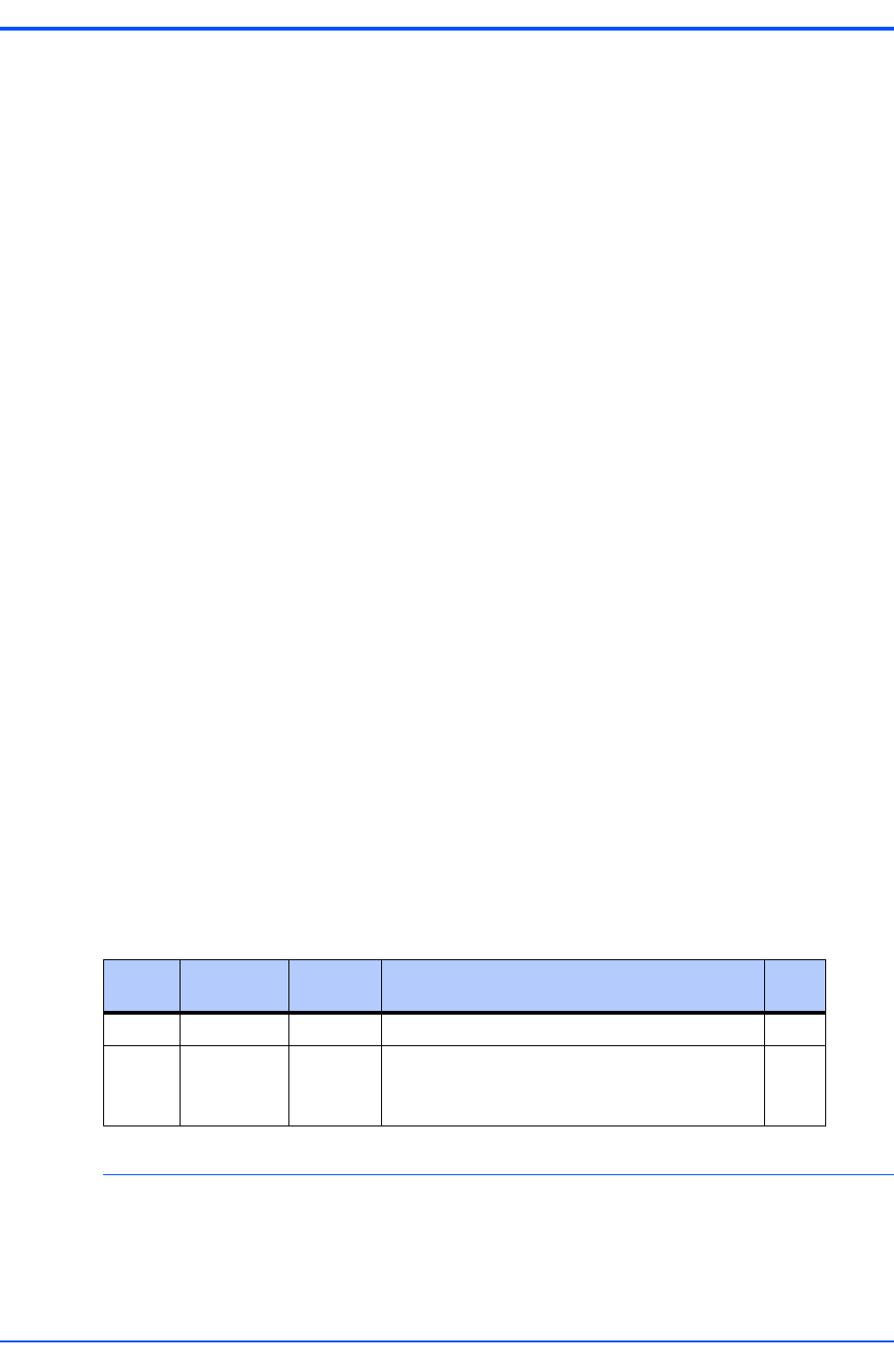

The Hawk interrupt assignments are shown below:

Notes

1. This interrupt provided for software compatibility with MVME2700.

Table 3-6. Hawk MPIC Interrupt Assignments

MPICI

RQ

Edge/Leve

l

Polarity Interrupt Source

Note

s

IRQ0 Level High PIB (8259) in PMC Slot 1 1

IRQ9 Level Low SCSI Controller interrupt shall be connected to

INTA# pin J11-04

2