RTC - 4543 SA/SB

Page - 8 MQ - 252 - 03

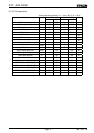

7-3. Data writes (Divider Reset)

CLK

WR

DATA

s40s20s10s8s4 y8 y10 y20 y40

CE

y80

1 522

N Seconds

s1

Divider reset

Pulse

s2

Timer,counter

N seconds

N seconds0 seconds

Carry stop

Pulse

After the counter is reset, carries to the seconds digit are halted.After the data write operation,

the prohibition on carries to the seconds counter is lifted by setting the CE pin low.

Complete data write operations within tCE (Max.) = 0.9 seconds, as described earlier.

7-4. FOUT output and 1 Hz carries

CLK

WR

CE

1Hz

FOUT

CLK

t

CES

t

1.0 s

0

-7.8 ms

15.6 ms 15.6 ms

During a data write operation, because a reset is applied to the Devider counter (from the 128 Hz

level to the 1 Hz level) after the CE pin goes high during the time between the falling edge of the first

clock cycle and the rising edge of the second clock cycle, the length of the first 1 Hz cycle after the

data write operation is 1.0 s

+0 /

−

7.8ms

+

t

CES

+

t

CLK.

Subsequent cycles are output at 1.0-second intervals.

The 1-Hz signal that is output on FOUT is the internal 1-Hz signal with a 15.6-ms shift applied.