Product Facts ⏐ Issue: June 01, 2008 ⏐ Product: SPARC

®

Enterprise M5000 Page 23 / 38

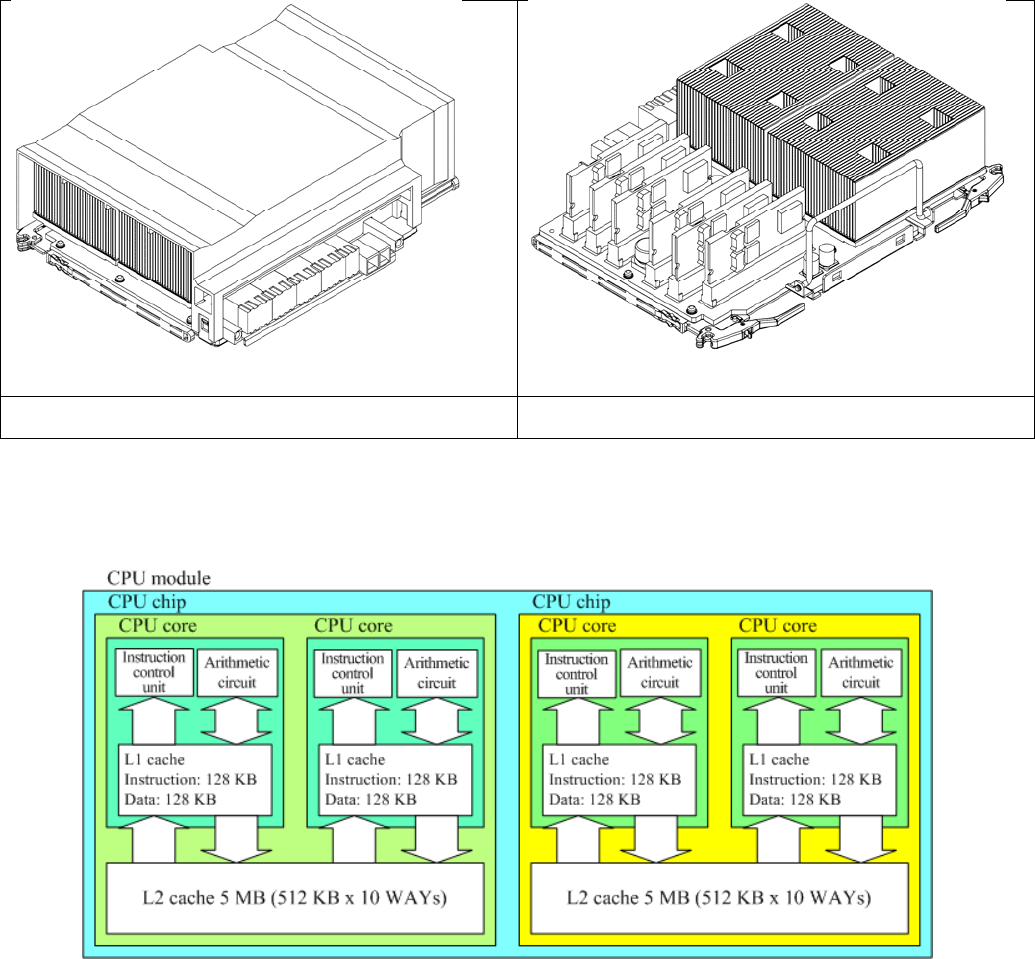

CPU Module

Product Overview

SPARC

®

ENTERPRISE M5000 servers use SPARC

®

64 VI processors, which are multi-core/multi-threading CPUs.

Each module contains two CPU chips (4 cores). Up to four CPU modules can be installed in SPARC

®

ENTERPRISE

M5000.

Appearance

CPU module for M4000/M5000 CPU module without cover viewed from the reverse side

Features

90 nm copper wiring CMOS technology is used for these processors to provide high performance while achieving low

power consumption.

Two CPU cores are built on each CPU chip using CMP (Chip Multi-Processing) technology.

CMT (Chip Multi-Threading) technology provides multi-thread processing that virtualizes each CPU core as two

threads.

The use of register renaming, out-of-order execution and non-blocking cache memory ensures high parallel-processing

performance.

These modules offer mainframe levels of reliability inherited from SPARC

®

64 V.

• • Data in both primary and secondary caches are protected by ECC (Error Checking and Correction).

• • Registers and ALU are protected by parity.

• • If an error occurs, the hardware re-executes the instruction that triggered the error.

(Not all errors are covered by this feature.)

• • If recoverable errors occur frequently in cache, hardware-set degrade mode is automatically invoked.