5.3 Host Commands

C141-E042-01EN 5-45

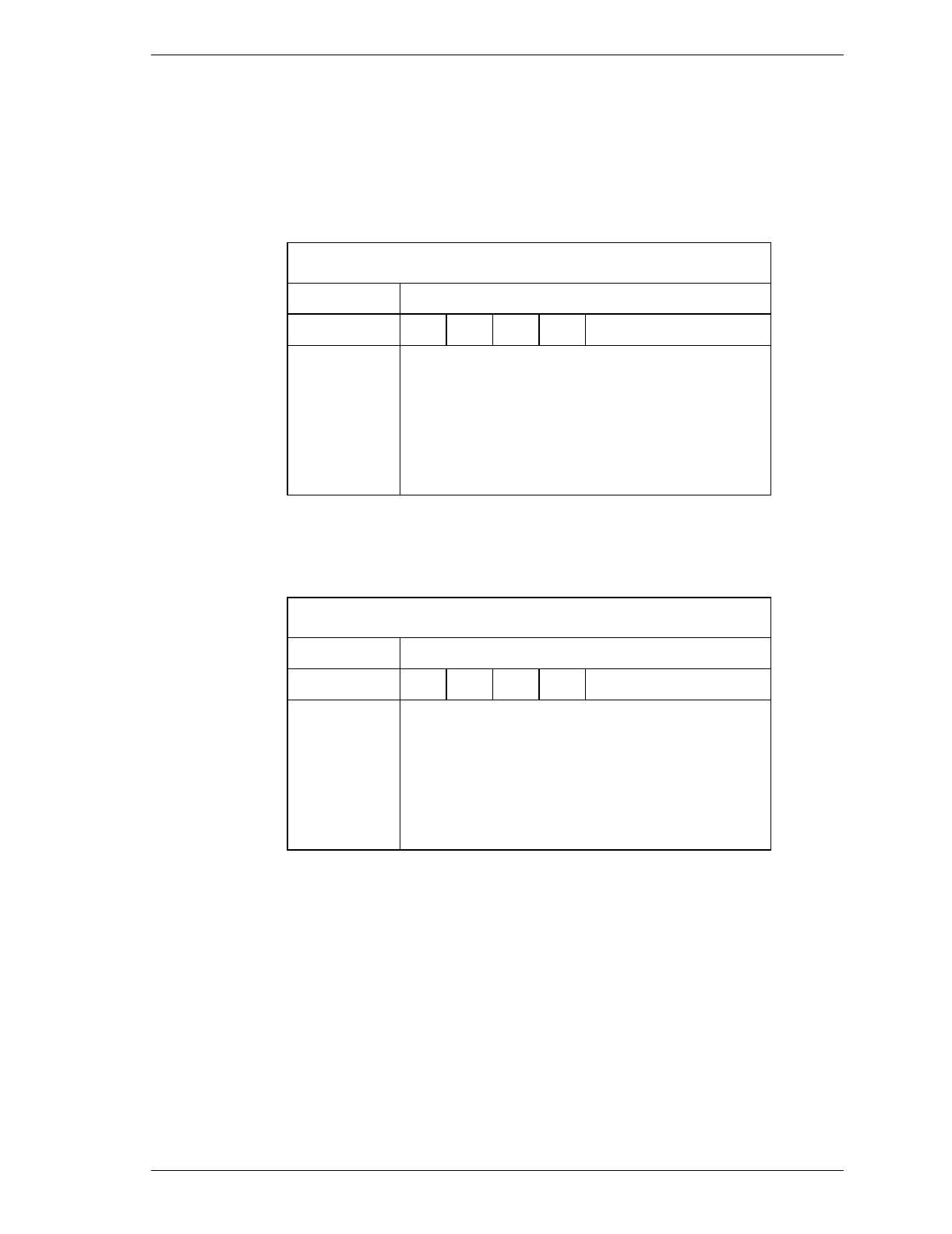

This command is operated under the following conditions:

•

The command is issued in a sequence of the READ LONG or WRITE LONG

(to the same address) command issuance. (WRITE LONG command can be

continuously issued after the READ LONG command.)

If above condition is not satisfied, the command operation is not guaranteed.

At command issuance (I/O registers setting contents)

1F7

H

(CM) 0011001R

1F6

H

(DH)

×

L

×

DV Head No. /LBA [MSB]

1F5

H

(CH)

1F4

H

(CL)

1F3

H

(SN)

1F2

H

(SC)

1F1

H

(FR)

Cylinder No. [MSB] / LBA

Cylinder No. [LSB] / LBA

Sector No. / LBA [LSB]

01

xx

R = 0 →with Retry

R = 1 →without Retry

At command completion (I/O registers contents to be read)

1F7

H

(ST) Status information

1F6

H

(DH)

×

L

×

DV Head No. /LBA [MSB]

1F5

H

(CH)

1F4

H

(CL)

1F3

H

(SN)

1F2

H

(SC)

1F1

H

(ER)

Cylinder No. [MSB] / LBA

Cylinder No. [LSB] / LBA

Sector No. / LBA [LSB]

00 (*1)

Error information

*1 If the command is terminated due to an error, this register indicates 01.

(19) READ BUFFER (X’E4’)

The host system can read the current contents of the sector buffer of the device by

issuing this command. Upon receipt of this command, the device sets the BSY bit

of Status register and sets up the sector buffer for a read operation. Then the

device sets the DRQ bit of Status register, clears the BSY bit, and generates an

interrupt. After that, the host system can read up to 512 bytes of data from the

buffer.