5.3 Host Commands

C141-E050-02EN 5-51

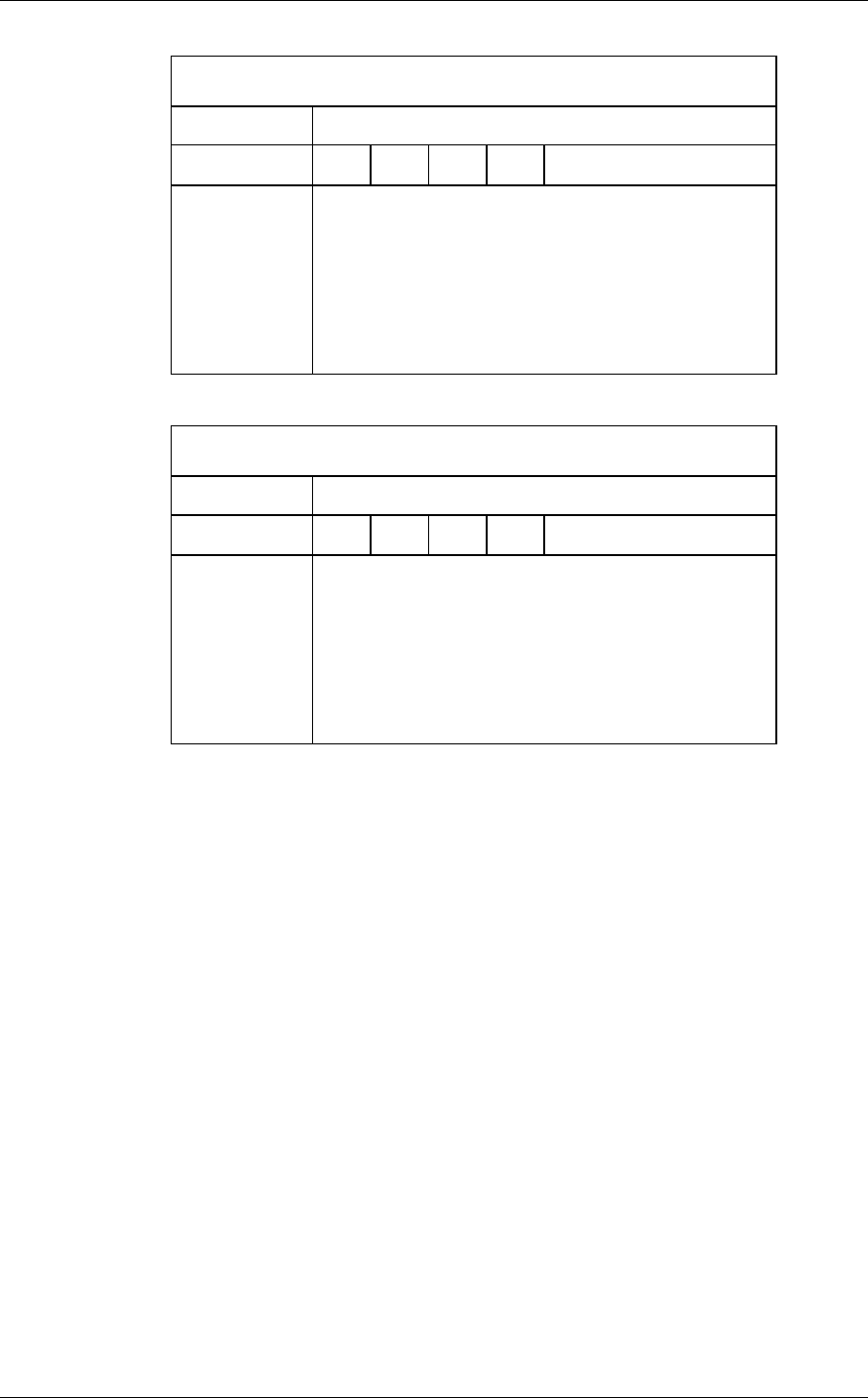

At command issuance (I/O registers setting contents)

1F7

H

(CM)

X’94’ or X’E0’

1F6

H

(DH)

× × ×

DV

xx

1F5

H

(CH)

1F4

H

(CL)

1F3

H

(SN)

1F2

H

(SC)

1F1

H

(FR)

xx

xx

xx

xx

xx

At command completion (I/O registers contents to be read)

1F7

H

(ST)

Status information

1F6

H

(DH)

× × ×

DV

xx

1F5

H

(CH)

1F4

H

(CL)

1F3

H

(SN)

1F2

H

(SC)

1F1

H

(ER)

xx

xx

xx

xx

Error information

(25) SLEEP (X’99’ or X’E6’)

This command is the only way to make the device enter the sleep mode.

Upon receipt of this command, the device sets the BSY bit of the Status register

and enters the sleep mode. The device then clears the BSY bit and generates an

interrupt. The device generates an interrupt even if the device has not fully entered

the sleep mode.

In the sleep mode, the spindle motor is stopped and the ATA interface section is

inactive. All I/O register outputs are in high-impedance state.

The only way to release the device from sleep mode is to execute a software or

hardware reset.