14

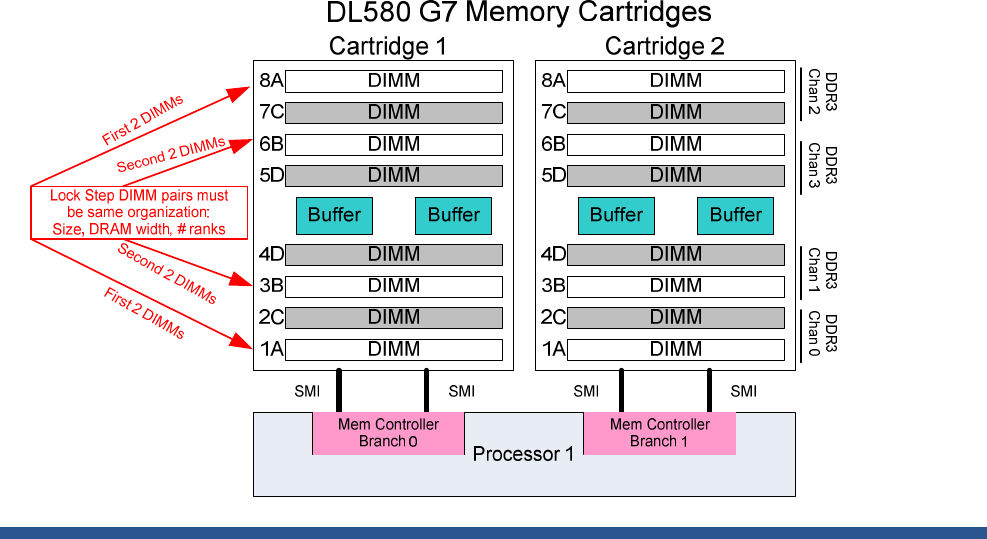

In memory expansion architecture, each processor has two embedded memory controllers. Each memory controller

controls two high-speed scalable memory interfaces (SMI). Each SMI link expands to two DDR3 buses via a scalable

memory buffer (SMB). Each memory controller runs its two SMI links in lockstep. Memory expansion architecture

furnishes a level of fault tolerance to sustain the failure of any DRAM device within any pair of lockstep DIMMs.

This memory subsystem design supplies enhanced performance in Advanced ECC mode. Additional memory

protection comes through online spare, mirrored memory and DDDC modes.

The DL580 G7 Advanced ECC supports up to 2TB of active memory utilizing 32 GB DDR3 RDIMMs. The server

provides notification if the level of correctable errors exceeds a pre-defined threshold. Standard ECC can only

correct single-bit memory errors. Advanced ECC corrects any single-bit and multi-bit memory error associated with a

single DRAM device (SDDC).

Online spare memory gives additional protection against degrading DIMMs. For example, rank sparing allows the

allocation of a rank in a DIMM as the online spare memory for a collection of two DIMMs. If one of the non-spare

DIMMs exceeds a threshold for correctable memory errors, the server automatically copies the contents of the

degraded memory to the online spare rank. Then the server deactivates the failing memory rank, and automatically

switches over to the online spare rank. This reduces the likelihood of uncorrectable memory errors, which could

result in server downtime. Online spare memory protection is available without any operating system support.

Mirrored memory protects against failed DIMMs. It supports up to 1 TB of active memory and 1 TB of mirrored

memory using 32-GB DIMMs. Within each processor, mirroring occurs on the memory controller level. Note that

each memory controller supports two SMI links. When two memory controllers mirror each other, DIMM pairs

associated with each memory controller maintain a copy of all memory contents. Memory writes go to DIMM pairs

of both memory controllers. Memory reads come from only one set of DIMM pairs of the two memory controllers,

unless an uncorrectable error occurs. If a memory read on one DIMM pair returns incorrect data due to an

uncorrectable memory error, the system automatically retrieves the correct data from the mirrored DIMM pair.

Systems do not lose mirroring protection because of transient and soft uncorrectable errors and maintain mirroring

protection unless memory in both DIMM pairs fail.