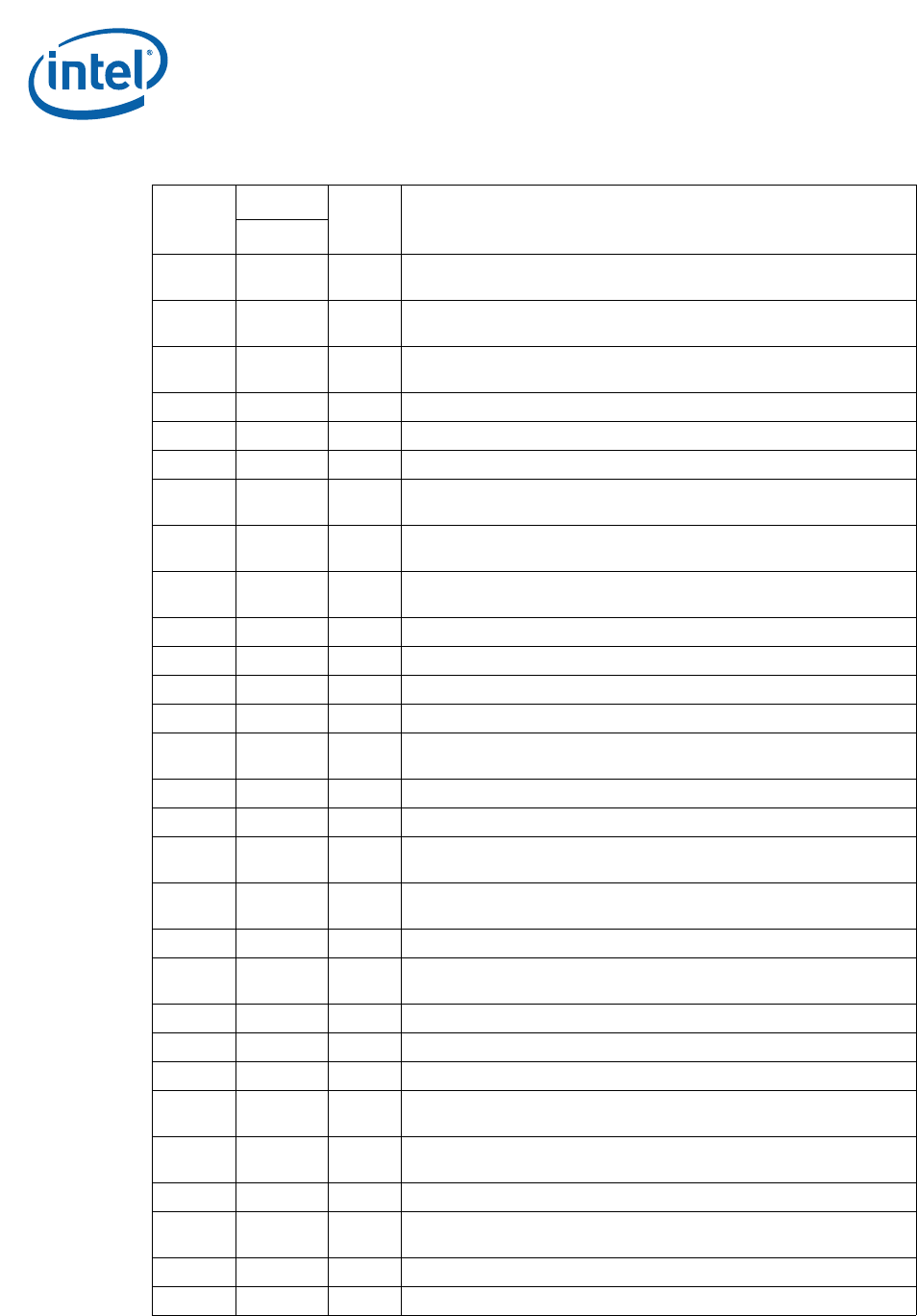

10 Specification Update

HSD26

XNo Fix

Specific Graphics Blitter Instructions May Result in Unpredictable

Graphics Controller Behavior

HSD27

XNo Fix

Processor May Enter Shutdown Unexpectedly on a Second

Uncorrectable Error

HSD28

XNo Fix

Modified Compliance Patterns for 2.5 GT/s and 5 GT/s Transfer Rates Do

Not Follow PCIe* Specification

HSD29

XNo FixPerformance Monitor Counters May Produce Incorrect Results

HSD30

XNo FixPerformance Monitor UOPS_EXECUTED Event May Undercount

HSD31

XNo FixMSR_PERF_STATUS May Report an Incorrect Core Voltage

HSD32

XNo Fix

PCIe* Atomic Transactions From Two or More PCIe Controllers May

Cause Starvation

HSD33

XNo Fix

The Corrected Error Count Overflow Bit in IA32_ MC0_STATUS is Not

Updated After a UC Error is Logged

HSD34

XNo Fix

An AVX Gather Instruction That Causes an EPT Violation May Not

Update Previous Elements

HSD35

XNo FixPLATFORM_POWER_LIMIT MSR Not Visible

HSD36

XNo FixLPDDR Memory May Report Incorrect Temperature

HSD37

XNo FixPCIe* Host Bridge DID May Be Incorrect

HSD38

XNo FixTSC May be Incorrect After a Deep C-State Exit

HSD39

XNo Fix

PCIe* Controller May Initiate Speed Change While in DL_Init State

Causing Certain PCIe Devices to Fail to Train

HSD40

XNo FixSpurious VT-d Interrupts May Occur When the PFO Bit is Set

HSD41

XNo FixN/A. Erratum has been removed.

HSD42

XNo Fix

AVX Gather Instruction That Causes a Fault or VM Exit May Incorrectly

Modify Its Destination Register

HSD43

XNo Fix

Inconsistent NaN Propagation May Occur When Executing (V)DPPS

Instruction

HSD44

XNo FixDisplay May Flicker When Package C-States Are Enabled

HSD45

XNo Fix

Certain Combinations of AVX Instructions May Cause Unpredictable

System Behavior

HSD46

XNo FixProcessor May Incorrectly Estimate Peak Power Delivery Requirements

HSD47

XNo FixIA32_PERF_CTL MSR is Incorrectly Reset

HSD48

XNo FixProcessor May Hang During a Function Level Reset of the Display

HSD49

XNo Fix

AVX Gather Instruction That Should Result in #DF May Cause

Unexpected System Behavior

HSD50

XNo Fix

Throttling and Refresh Rate Maybe be Incorrect After Exiting Package C-

State

HSD51

XNo FixProcessor May Livelock During On Demand Clock Modulation

HSD52

XNo Fix

IA32_DEBUGCTL.FREEZE_PERFMON_ON_PMI is Incorrectly Cleared

by SMI

HSD53

XNo FixThe From-IP for Branch Tracing May be Incorrect

HSD54

XNo FixTM1 Throttling May Continue indefinitely

Errata (Sheet 2 of 5)

Number

Steppings

Status ERRATA

C-0