8

www.st.com/micropsd

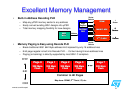

• 8051s typically cannot write to “code” space

– Special µPSD register eliminates this limitation

• Typical Flash memory cannot be read and written

at the same time

– Dual Banks of Flash eliminate this limitation

– Read program from one bank while writing to the other bank

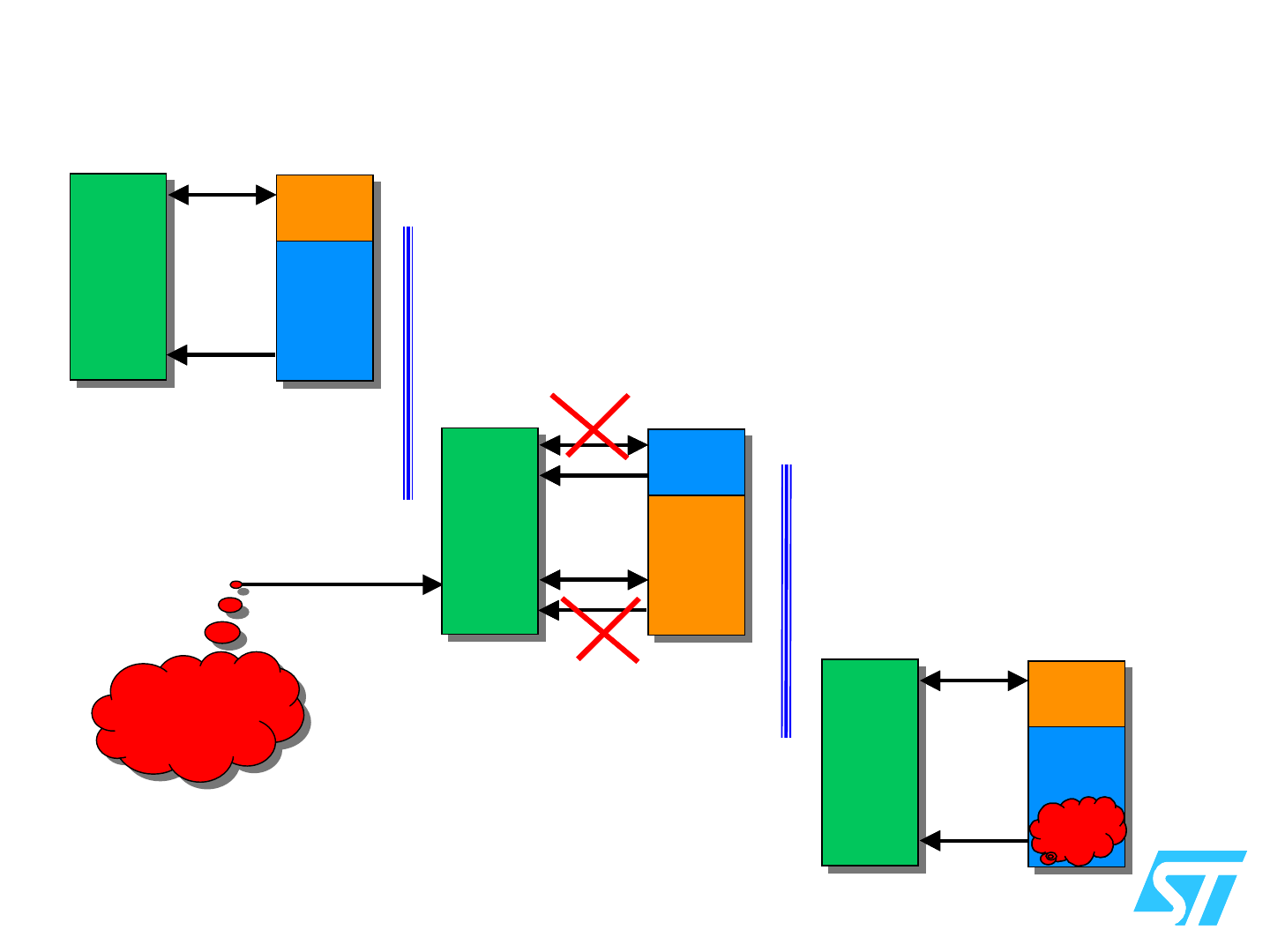

Remote Field Updates with IAP

Remote Field Updates with IAP

3. After IAP

2. During IAP

1. Before IAP

• Special Register temporarily re-

classifies Main Flash as Data

• MCU now reads IAP program

from 2

nd

Flash while receiving

bytes of new program from

USB, UART, Modem, I

2

C, etc.

and writes the new program to

Main Flash

• Special Register classifies

Main Flash as Code again

• MCU now reading new

program from Main Flash

• MCU reading program

from Main Flash

USB, UART,

I

2

C, Modem…

Updated

Updated

Program

Program

MAIN

MAIN

FLASH

FLASH

OLD

OLD

CODE

CODE

2

2

nd

nd

Flash

Flash

DATA

DATA

8032

8032

MCU

MCU

READ &

WRITE

READ

ONLY

MAIN

MAIN

FLASH

FLASH

OLD

OLD

CODE

CODE

2

2

nd

nd

Flash

Flash

DATA

DATA

8032

8032

MCU

MCU

READ &

WRITE

READ

ONLY

READ

ONLY

MAIN

MAIN

FLASH

FLASH

TREAT

TREAT

AS DATA

AS DATA

2

2

nd

nd

Flash

Flash

CODE

CODE

8032

8032

MCU

MCU

READ &

WRITE

READ

ONLY

READ

ONLY

READ &

WRITE

MAIN

MAIN

FLASH

FLASH

TREAT

TREAT

AS DATA

AS DATA

2

2

nd

nd

Flash

Flash

CODE

CODE

8032

8032

MCU

MCU

READ &

WRITE

READ &

WRITE

READ

ONLY

READ

ONLY

READ

ONLY

READ

ONLY

READ &

WRITE

READ &

WRITE

MAIN

MAIN

FLASH

FLASH

2

2

nd

nd

Flash

Flash

DATA

DATA

8032

8032

MCU

MCU

READ &

WRITE

READ

ONLY

NEW

NEW

CODE

CODE

MAIN

MAIN

FLASH

FLASH

2

2

nd

nd

Flash

Flash

DATA

DATA

8032

8032

MCU

MCU

READ &

WRITE

READ

ONLY

READ

ONLY

NEW

NEW

CODE

CODE

NEW

NEW

CODE

CODE