7.3.3 TRIGGER CONTROL/STATUS REGISTER

BADR1 + 4

This register provides control bits for all ADC trigger modes. A Read/Write register.

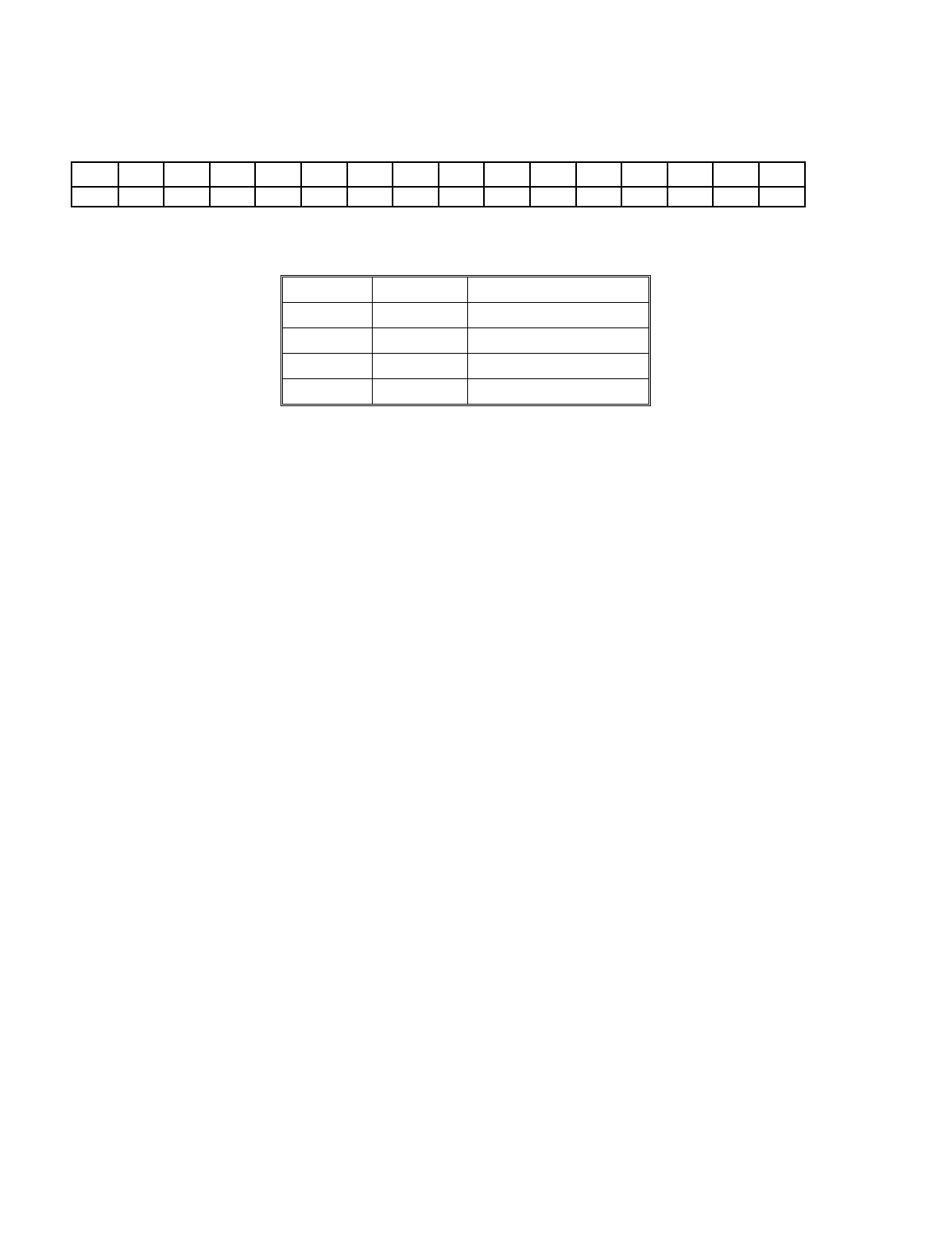

WRITE

TS0TS1--TGENBURSTEPRTRGXTRCL---ARMFFM0C0SRC--

0123456789101112131415

TS[1:0]

These bits select one-of-two possible ADC Trigger Sources:

Not Defined11

External (Digital)01

SW Trigger10

Disabled00

SourceTS0TS1

Note

: TS[1:0] should be set to 0 while setting up Pacer source and count values.

TGEN

This bit is used to enable External Trigger function

1 = External rising-edge Digital Trigger enabled.

0 = External Digital Trigger has no effect.

Note that the external trigger requires proper setting of the

TS[1:0]

and

TGEN

bits. Once these bits are set, the next rising edge will start a Paced ADC conversion.

Subsequent triggers will have no effect until external trigger flop is cleared (

XTRCL

).

BURSTE

This bit enables 330KHz ADC Burst mode. Start/Stop channels are selected via

the CHLx, CHHx bits in ADC CTRL/STAT register at BADR1 + 2.

1 = Burst Mode enabled

0 = Burst Mode disabled

PRTRG

This bit enables ADC Pre-trigger Mode. This bit works with the ARM and FFM0

bits when using Pre-trigger mode. See document "PCI-DAS1000 ADC Modes"

for programming guidelines.

1 = Enable Pre-trigger Mode

0 = Disable Pre-trigger Mode

XTRCL

A write-clear to reset the

XTRIG

flip-flop.

1 = Clear

XTRIG

status.

0 = No Effect.

ARM,

FFM0

These bits works in conjunction with

PRTRG

during FIFO'd ADC operations.

See document "PCI-DAS1000 ADC Modes" for programming guidelines.

21