Pico E-15 Hardware Reference

www.picocomputing.com

Pico Computing

(206) 283-2178

150 Nickerson Street. Suite 311

Seattle, WA 98109

25

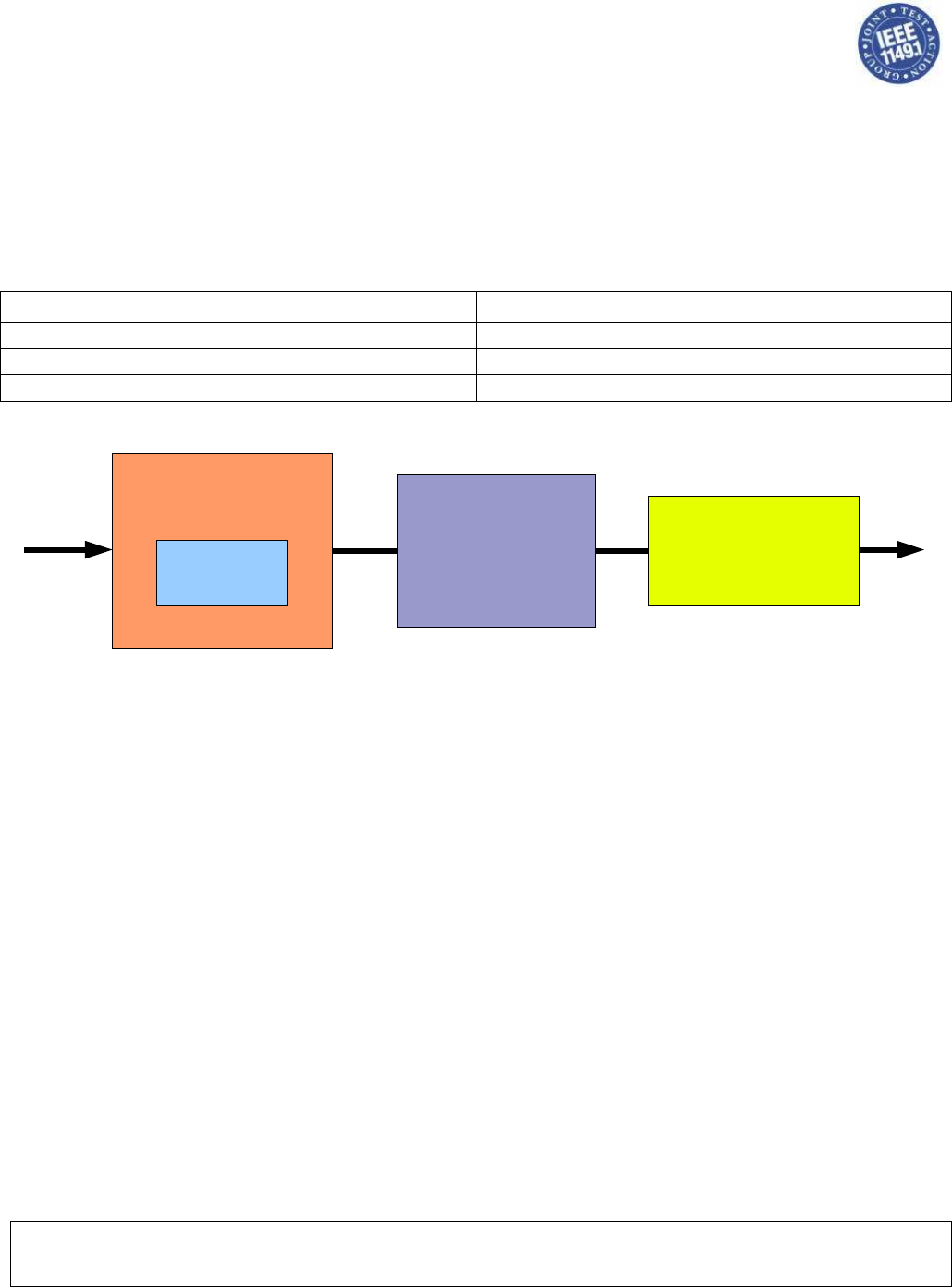

JTAG Debug Interface

The Pico E-15 is equipped with a JTAG diagnostic port which allows real-time debugging of

hardware, firmware and software.

Some JTAG programs require the length of the instruction register (IR). The IR length is listed

below for all devices in the JTAG chain. The FPGA IR length changes depending on how

many PowerPCs are internally connected to the JTAG chain in the FPGA.

Device Instruction register bit length

FPGA 6,10 or 14 (Depends on PPC Configuration)

TurboLoader 8

Ethernet PHY 8

FPGA

PowerPC

IR= 10

EthernetTurbo Loader

TDI TDO

IR= 8

IR= 8

The Primary Image in the Flash ROM contains an embedded JTAG diagnostic port. This

allows a user in Windows or Linux to debug software without an external JTAG cable. The

internal JTAG diagnostic loopback looks just like a Parallel Port JTAG diagnostic cable when

used with the Pico E-15 driver.

The external JTAG interface uses 1.8V logic.