18

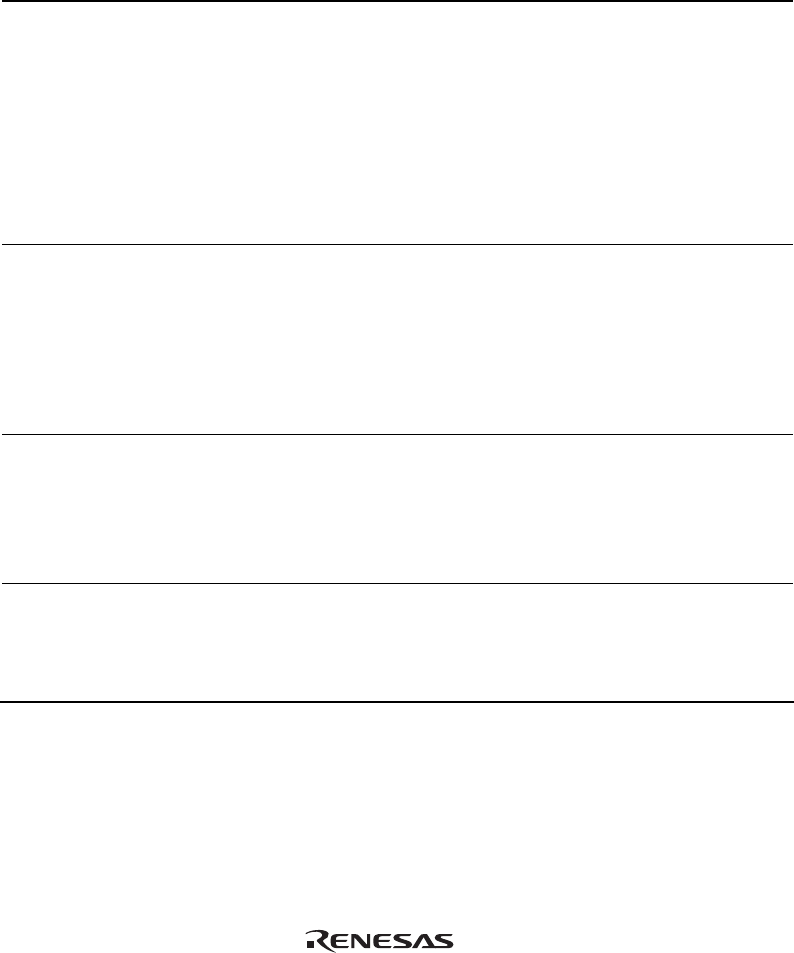

8. Operation while Cache is Enabled

When cache is enabled, the emulator operates as shown in table 2.4.

Table 2.4 Operation while Cache is Enabled

Function Operation Notes

Memory write Searches for whether or not the address to be

written hits the instruction and operand caches.

• When the address hits, the corresponding

position of the data array is changed by the

data to be written and single write is

performed to the external area.

• When the address does not hit, the cache

contents are not changed and single write is

performed to the external area.

• The contents of the

address array are not

changed before or

after writing of

memory.

Memory read Searches for whether or not the address to be

read hits the operand cache.

• When the address hits, the corresponding

position of the data array is read.

• When the address does not hit, single write

is performed to the external area.

• The instruction cache

is not searched for.

• The contents of the

address array are not

changed before or

after reading of

memory.

BREAKPOINT Clears the V and LRU bits of all entries in the

instruction cache to 0 if a BREAKPOINT is set

or canceled.

Clears the V and LRU bits of all entries in the

instruction cache to 0 if a break occurs when a

BREAKPOINT has been set.

• Use the Event

Condition if you do not

wish to change the

contents of the

instruction cache.

Program load Writes the contents of the data cache to the

external memory and clears the V and LRU bits

of entries in the instruction and data caches to

0 after loading of the program has been

completed.

If memory is read from or written to the disabled cache area, cache is not searched for but the

external area is accessed.