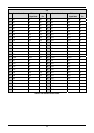

JA2

Pin Generic Header Name CPU board

Signal Name

Device

Pin

Pin Generic Header Name CPU board

Signal Name

Device

Pin

1 RESn RESn 70 2 EXTAL CON_EXTAL 72

3 NMIn NMI 73 4 VSS1 GROUND -

5 WDT_OVF WDT_OVFn 100 6 SCIaTX TxD0 68

7 IRQ0 IRQ0 46 8 SCIaRX RxD0 69

9 IRQ1 IRQ1 45 10 SCIaCK SCK0 67

11 UD UD 49 12 CTSRTS NC -

13 Up M1_Up 17 14 Un M1_Un 15

15 Vp M1_Vp 13 16 Vn M1_Vn 10

17 Wp M1_Wp 12 18 Wn M1_Wn 9

19 TMR0 TMR0 23 20 TMR1 TMR1 22

21 TRIGa TRIGa 21 22 TRIGb TRIGb 20

23 IRQ2 IRQ2 44 24 TRISTn TRISTn 30

25 - NC - 26 - NC -

Table 9-6: JA2 Standard Generic Header

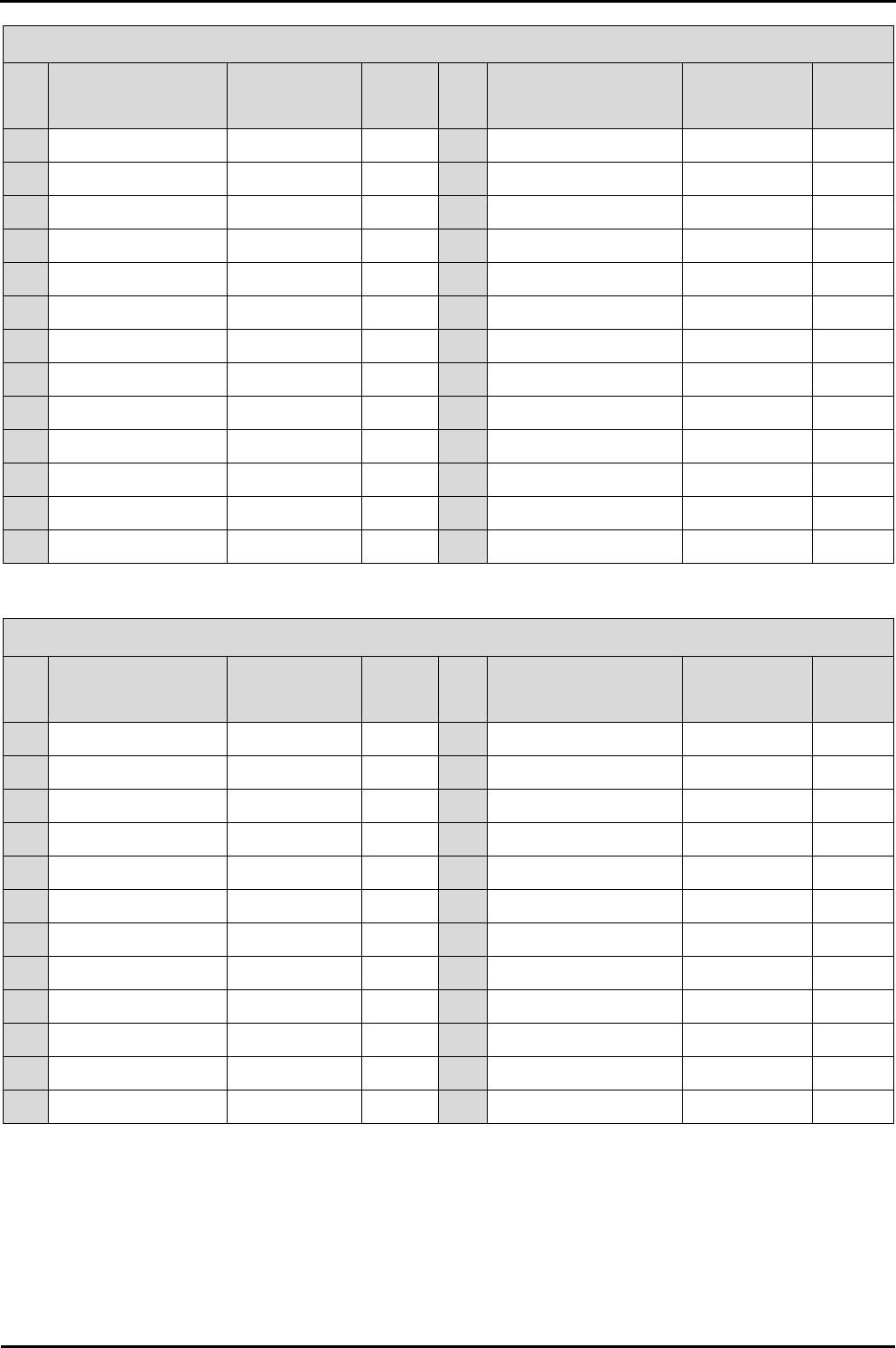

JA5

Pin Generic Header Name CPU board

Signal Name

Device

Pin

Pin Generic Header Name CPU board

Signal Name

Device

Pin

1 AD4 AN4 92 2 AD5 AN5 91

3 AD6 AN6 90 4 AD7 AN7 89

5 CAN1TX CTx0 42 6 CAN1RX CRx0 41

7 CAN2TX NC - 8 CAN2RX NC -

9 AD8 AN12 83 10 AD9 AN13 82

11 AD10 AN14 81 12 AD11 AN15 80

13 TIOC0A NC - 14 TIOC0B NC -

15 TIOC0C NC - 16 M2_TRISTn M2_TRISTn 47

17 TCLKC NC - 18 TCLKD NC -

19 M2_Up M2_Up 8 20 M2_Un M2_Un 7

21 M2_Vp M2_Vp 6 22 M2_Vn M2_Vn 4

23 M2_Wp M2_Wp 5 24 M2_Wn M2_Wn 2

Table 9-7: JA5 Standard Generic Header

28