SH7263/SH7203 Group

Data Transfer to On-chip Peripheral Modules with DMAC

REJ06B0734-0100/Rev.1.00 April 2008 Page 4 of 17

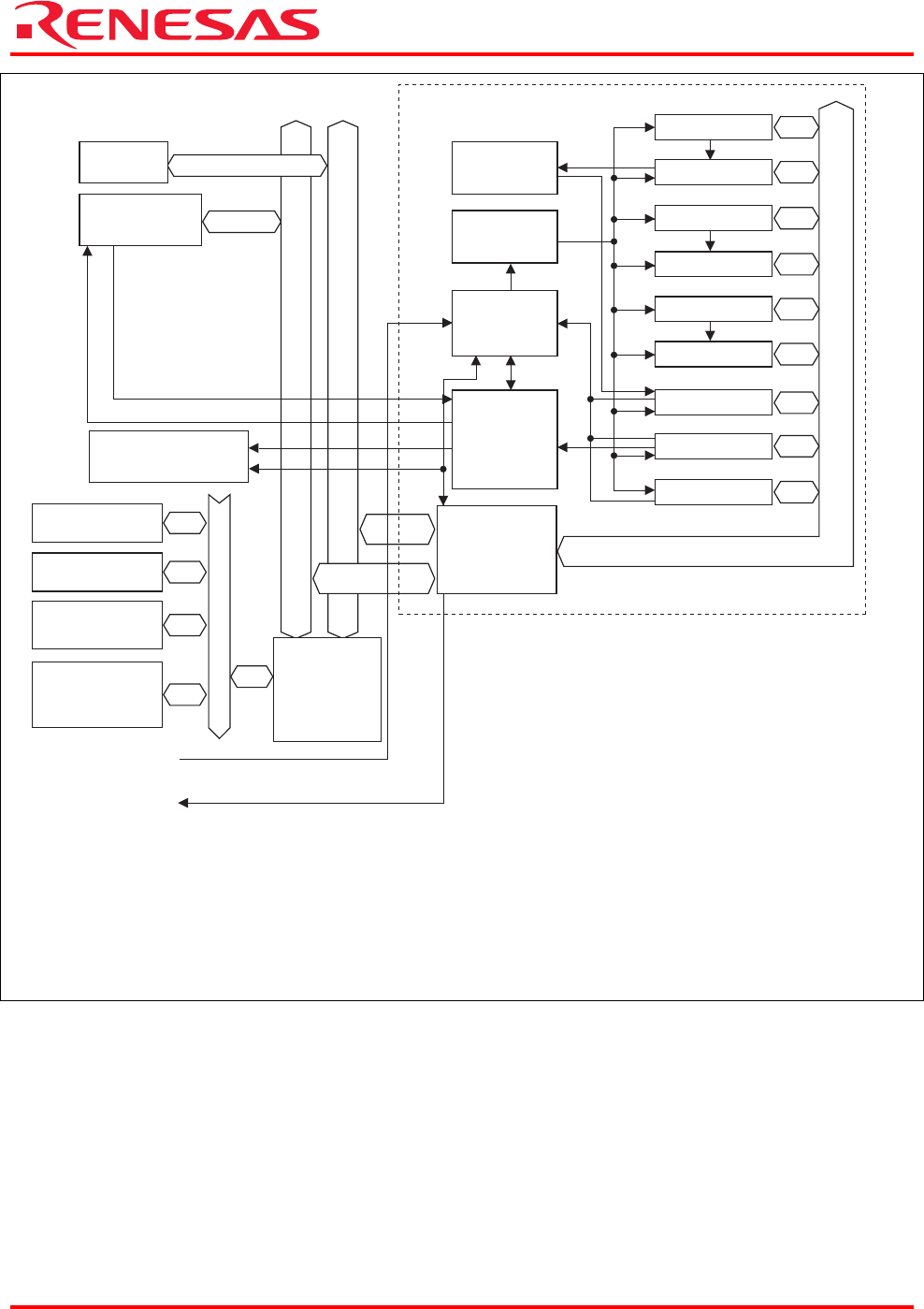

DMATCR_n

SAR_n

CHCR_n

DAR_n

DMAOR

DMARS0 to DMARS3

HEIn

DACK0 to DACK3,

TEND0, TEND1

DEIn

RDMATCR_n

RSAR_n

RDAR_n

On-chip

memory

On-chip

peripheral

module

DMA transfer

request signal

DMA transfer acknowledge signal

Interrupt controller

External ROM

External RAM

External device

(memory mapped)

External device

(with acknowledge)

DREQ0 to DREQ3

Peripheral bus

Internal bus

DMAC module

Iteration

control

Register

control

Start-up

control

Request

priority

control

Bus

interface

Bus state

controller

[Legend]

RDMATCR: DMA reload transfer count register CHCR: DMA channel control register

DMATCR: DMA transfer count register DMAOR: DMA operation register

RSAR: DMA reload source address register DMARS0 to DMARS3: DMA extension resource selectors 0 to 3

SAR: DMA source address register HEIn: DMA transfer half-end interrupt request to the CPU

RDAR: DMA reload destination address register DEIn: DMA transfer end interrupt request to the CPU

DAR: DMA destination address register n: 0, 1, 2, 3, 4, 5, 6, 7

Figure 1 Block Diagram of DMAC