SH7263/SH7203 Group

Data Transfer to On-chip Peripheral Modules with DMAC

REJ06B0734-0100/Rev.1.00 April 2008 Page 7 of 17

2.4 Processing Procedure of Sample Program

In this sample program, character string data stored in external memory are transferred by DMA to the transmit FIFO

data register (SCFTDR) on SCIF channel 0, and then are transmitted in UART mode.

The register settings for the sample program are listed in table 2. The macro definitions used in this sample program are

also listed in table 3. A flowchart of the sample program is illustrated in figure 4.

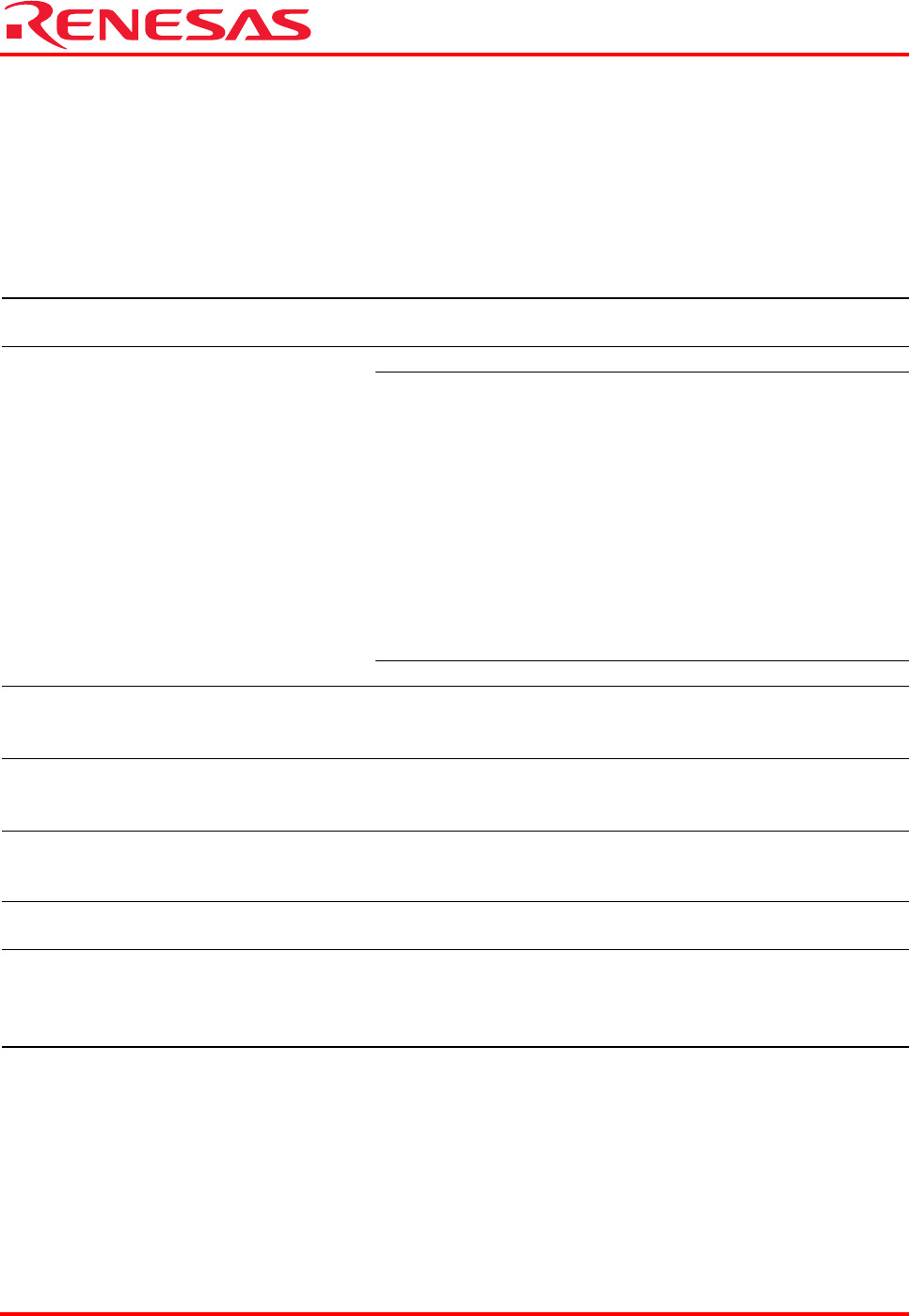

Table 2 Register Settings for Sample Program

Register Name Address Setting Value Description

Standby control

register 2 (STBCR2)

H'FFFE 0018 H'00 MSTP8 = "0": DMAC operates

H'0000 0000 DE = "0": Disables DMA transfer

H'0000 1800

TC = "0": Transfers data once for each

DMA transfer request

RLDSAE = "0":

Disables SAR reload function

RLDDAR = "0":

Disables DAR reload function

DM = "B'00": Fixes destination address

SM = "B'01": Increments source address

RS = "B'1000": Extension resource selector

TB = "0": Cycle-stealing mode

TS = "B'00": Byte transfer

IE = "0": Disables interrupt request

DMA channel control

register 1 (CHCR1)

H'FFFE 101C

H'0000 1801 DE = "1": Enables DMA transfer

DMA source address

register_1 (SAR1)

H'FFFE 1010

Address where

character string

data are stored

Start address of transfer source:

Start address of character string stored in

external memory

DMA destination

address register_1

(DAR1)

H'FFFE 1014 H'FFFE 800C

Start address of transfer destination:

Address of the SCIF transmit FIFO data

register_1 (SCFTDR_1)

DMA transfer count

register_1 (DMATCR1)

H'FFFE 1018

Number of

character string

data

Transfer count: the number of character

string data

DMA operation register

(DMAOR)

H'FFFE 1200 H'0001

DME = "1": Enables DMA transfer on all the

channels

DMA extension

resource selector

(DMARS0)

H'FFFE 1300 H'0081 MID = "B'100000"

RID = "B'01"

Set to SCIF_0 transmit FIFO data empty

transfer request