SH7263/SH7203 Group

Data Transfer to On-chip Peripheral Modules with DMAC

REJ06B0734-0100/Rev.1.00 April 2008 Page 6 of 17

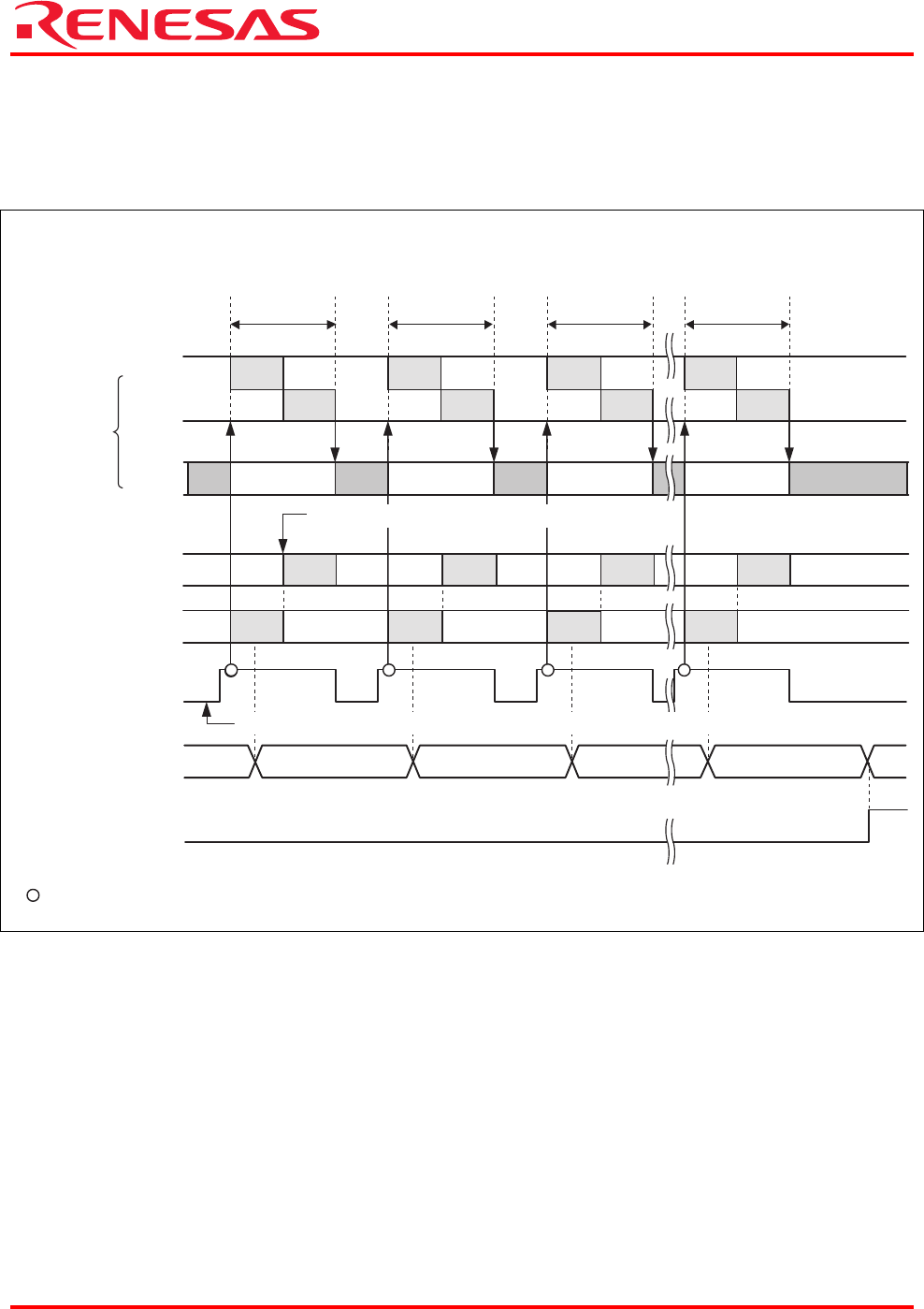

2.3 Operation of Sample Program

In this sample program, SCIF transmit FIFO data empty transfer requests are made to activate DMAC channel 1, and to

transfer data from external memory to the transmit FIFO data register (SCFTDR) on SCIF channel 0. The data written

to SCFTDR on SCIF channel 0 are transmitted in UART mode. An operation timing of the sample program is shown in

figure 3.

DMAC1

CPU

H'28H'29

H'27 H'00

One data

transfer

DMA transfer using SCIF transmit FIFO data empty transfer requests

(Timing of requesting data transfer from external memory to the SCIF transmit FIFO data register: a

transfer request is made when the number of data in transmit FIFO becomes 0)

One data

transfer

One data

transfer

One data

transfer

Bus

mastership

Read Read Read Read

Read Read Read Read

Write Write Write Write

Write Write Write Write

Internal signal Internal signal Internal signal

Internal bus

External bus

DMA transfer request

(When the DMA master

enable bit is 1)

SCIF transmit FIFO data empty transfer request (on-chip peripheral request)

Write to SCIF transmit FIFO data register (SCFTDR)

DMA transfer count

register (DMATCR)

Transfer end flag (TE)

[Legend]

: DMA request acknowledge

Figure 3 Operation Timing of Sample Application