S3C8275X/F8275X/C8278X/F8278X/C8274X/F8274X INSTRUCTION SET

6-9

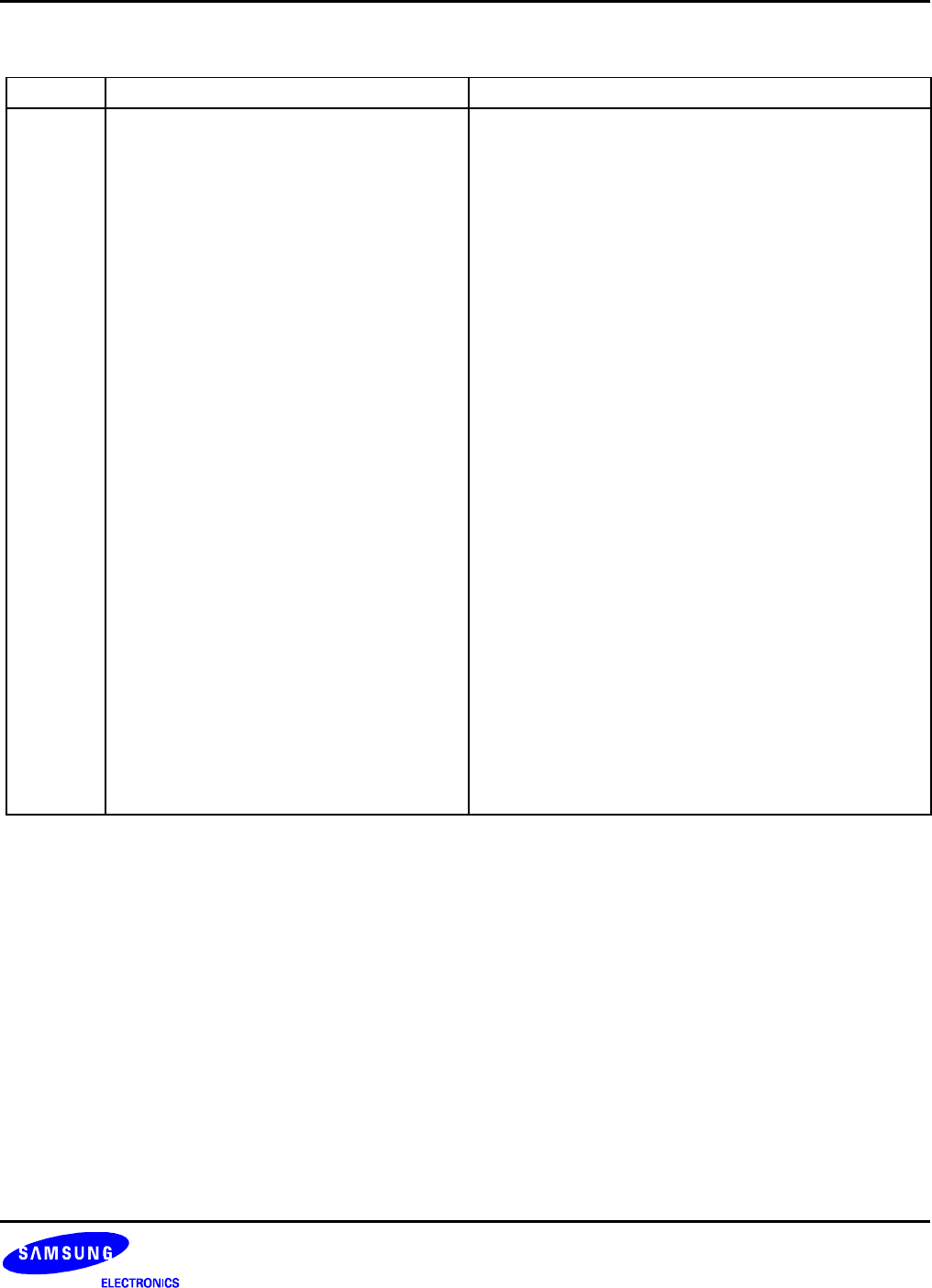

Table 6-4. Instruction Notation Conventions

Notation Description Actual Operand Range

cc Condition code See list of condition codes in Table 6-6.

r Working register only

Rn (n = 0−15)

rb Bit (b) of working register

Rn.b (n = 0−15, b = 0−7)

r0 Bit 0 (LSB) of working register

Rn (n = 0−15)

rr Working register pair RRp (p = 0, 2, 4, ..., 14)

R Register or working register

reg or Rn (reg = 0−255, n = 0−15)

Rb Bit 'b' of register or working register

reg.b (reg = 0−255, b = 0−7)

RR Register pair or working register pair

reg or RRp (reg = 0−254, even number only, where

p = 0, 2, ..., 14)

IA Indirect addressing mode addr (addr = 0–254, even number only)

Ir Indirect working register only

@Rn (n = 0−15)

IR Indirect register or indirect working register

@Rn or @reg (reg = 0−255, n = 0−15)

Irr Indirect working register pair only @RRp (p = 0, 2, ..., 14)

IRR Indirect register pair or indirect working

register pair

@RRp or @reg (reg = 0−254, even only, where

p = 0, 2, ..., 14)

X Indexed addressing mode

#reg [Rn] (reg = 0−255, n = 0−15)

XS Indexed (short offset) addressing mode

#addr [RRp] (addr = range −128 to +127, where

p = 0, 2, ..., 14)

xl Indexed (long offset) addressing mode

#addr [RRp] (addr = range 0−65535, where

p = 0, 2, ..., 14)

da Direct addressing mode

addr (addr = range 0−65535)

ra Relative addressing mode

addr (addr = number in the range +127 to −128 that is

an offset relative to the address of the next instruction)

im Immediate addressing mode

#data (data = 0−255)

iml Immediate (long) addressing mode

#data (data = range 0−65535)