- 20 -

datasheet DDR3L SDRAM

Rev. 1.0

Unbuffered DIMM

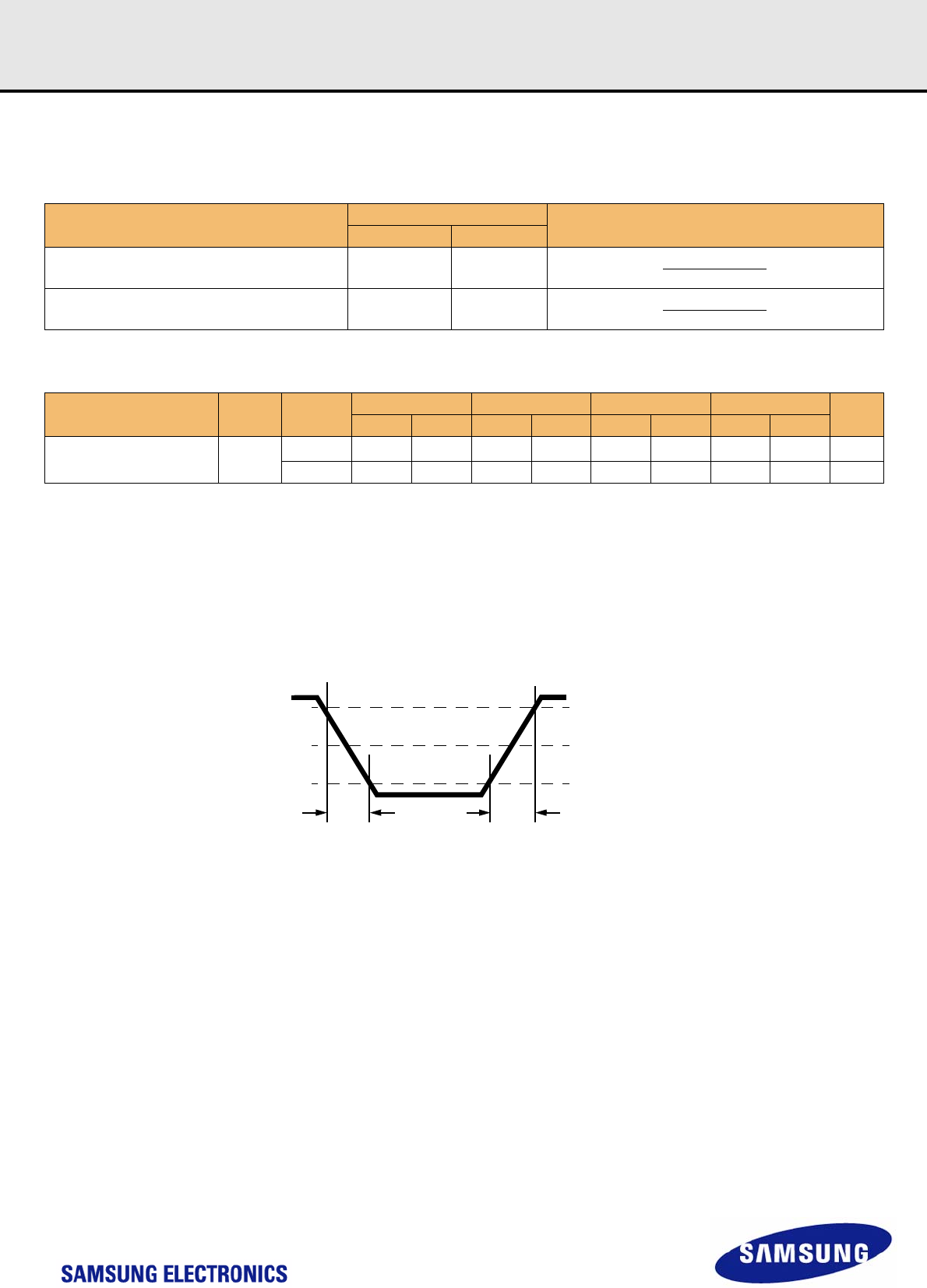

12.3 Single-ended Output Slew Rate

With the reference load for timing measurements, output slew rate for falling and rising edges is defined and measured between V

OL

(AC) and V

OH

(AC)

for single ended signals as shown in below.

[ Table 12 ] Single ended Output slew rate definition

NOTE : Output slew rate is verified by design and characterization, and may not be subject to production test.

[ Table 13 ] Single ended output slew rate

Description : SR : Slew Rate

Q : Query Output (like in DQ, which stands for Data-in, Query-Output)

se : Single-ended Signals

For Ron = RZQ/7 setting

NOTE : 1) In two cased, a maximum slew rate of 6V/ns applies for a single DQ signal within a byte lane.

- Case_1 is defined for a single DQ signal within a byte lane which is switching into a certain direction (either from high to low of low to high) while all remaining DQ

signals in the same byte lane are static (i.e they stay at either high or low).

- Case_2 is defined for a single DQ signals in the same byte lane are switching into the opposite direction (i.e. from low to high or high to low respectively). For the

remaining DQ signal switching into the opposite direction, the regular maximum limit of 5 V/ns applies.

Figure 7. Single-ended output slew rate definition

Description

Measured

Defined by

From To

Single ended output slew rate for rising edge

V

OL

(AC) V

OH

(AC)

V

OH

(AC)-V

OL

(AC)

Delta TRse

Single ended output slew rate for falling edge

V

OH

(AC) V

OL

(AC)

V

OH

(AC)-V

OL

(AC)

Delta TFse

Parameter Symbol

Operation

Voltage

DDR3-800 DDR3-1066 DDR3-1333 DDR3-1600

Units

Min Max Min Max Min Max Min Max

Single ended output slew rate SRQse

1.35V 1.75

5

1)

1.75

5

1)

1.75

5

1)

1.75

5

1)

V/ns

1.5V 2.5 5 2.5 5 2.5 5 2.5 5 V/ns

V

OHdiff

(AC)

V

OLdiff

(AC)

delta TRdiffdelta TFdiff

V

TT